THE · 80386 · BOOK

By Ross P. Nelson

Microsoft

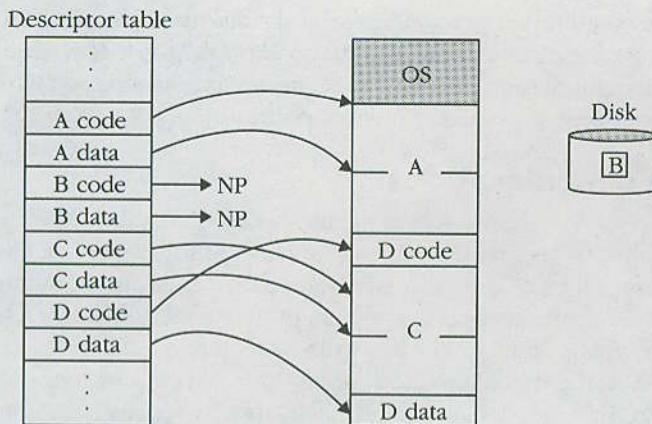

P R E S S

®

THE · 80386 · BOOK

# 80386

By Ross P. Nelson

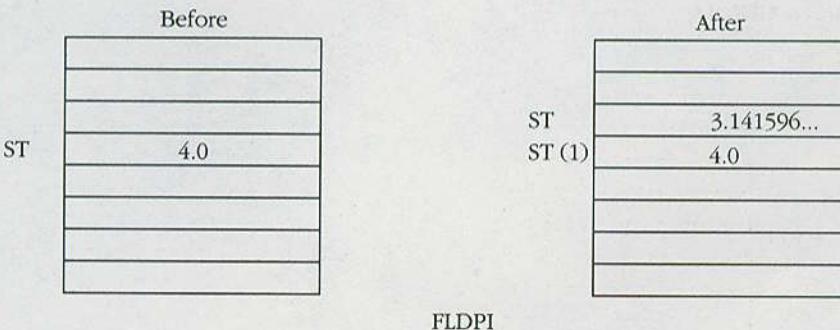

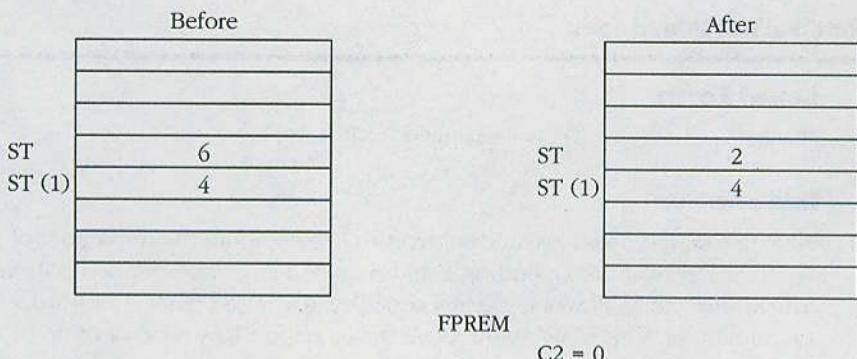

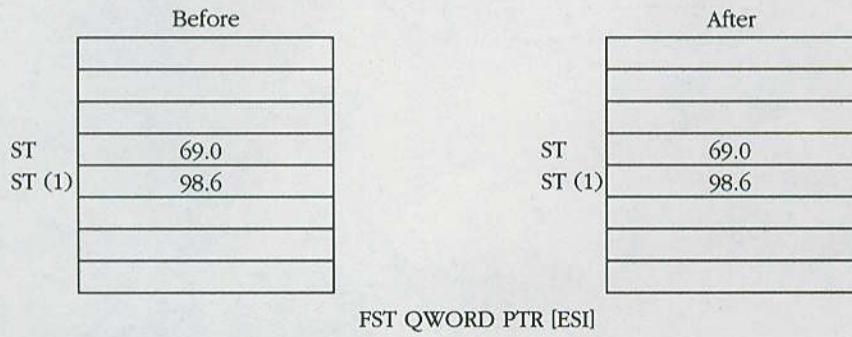

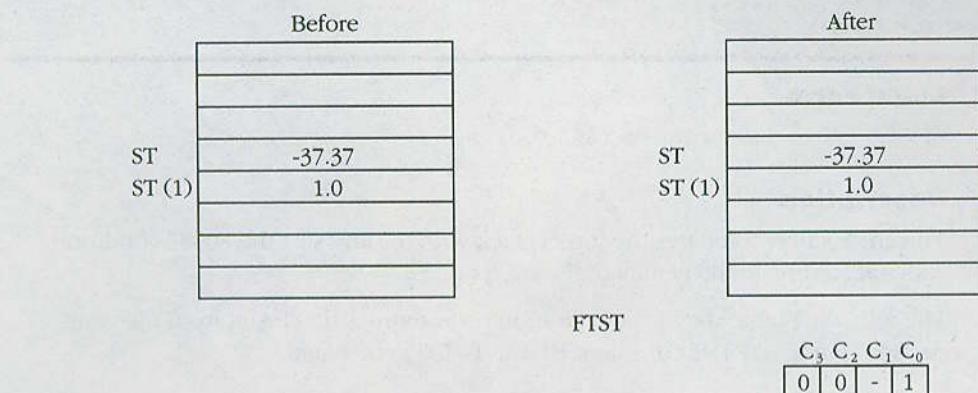

PUBLISHED BY

Microsoft Press

A Division of Microsoft Corporation

16011 NE 36th Way, Box 97017, Redmond, Washington 98073-9717

Copyright © 1988 by Ross P. Nelson

All rights reserved. No part of the contents of this book may

be reproduced or transmitted in any form or by any means without

the written permission of the publisher.

Library of Congress Cataloging in Publication Data

Nelson, Ross P., 1957-

The 80386 book: assembly language programmer's guide for the 80386/

Ross P. Nelson.

p. cm.

Includes index.

1. Intel 80386 (Microprocessor)—Programming. 2. Assembler language

(Computer program language) I. Title.

QA76.8.I2928N45 1988 88-21106

005.265—dc19 CIP

ISBN 1-55615-138-1

Printed and bound in the United States of America.

1 2 3 4 5 6 7 8 9 MLML 3 2 1 0 9 8

Distributed to the book trade in the United States by Harper & Row.

Distributed to the book trade in Canada by General Publishing Company, Ltd.

Distributed to the book trade outside the United States and Canada by Penguin Books Ltd.

Penguin Books Ltd., Harmondsworth, Middlesex, England

Penguin Books Australia Ltd., Ringwood, Victoria, Australia

Penguin Books N.Z. Ltd., 182-190 Wairau Road, Auckland 10, New Zealand

British Cataloging in Publication Data available

IBM® is a trademark of International Business Machines Corporation, Incorporated. Intel® is a registered trademark of Intel Corporation. Microsoft® and MS-DOS® are registered trademarks of Microsoft Corporation. All mnemonics copyright Intel Corporation 1986, 1987.

*To Robert and Ardell Nelson*

## Contents

|                                                     |           |

|-----------------------------------------------------|-----------|

| Introduction                                        | <i>xi</i> |

| <b>1</b> Evolution of the 80386 Architecture        | 1         |

| <b>2</b> The 80386 Architecture                     | 13        |

| <b>3</b> Memory Architecture: Segmentation          | 43        |

| <b>4</b> The 80386 Instruction Set                  | 63        |

| <b>5</b> The 80386 Protection Mechanism             | 93        |

| <b>6</b> Memory Architecture: Paging                | 125       |

| <b>7</b> Three in One                               | 135       |

| <b>8</b> The 80386/80387 Instruction Set Reference  | 147       |

| <b>Appendix A</b> Powers of Two                     | 381       |

| <b>Appendix B</b> ASCII Character Set               | 383       |

| <b>Appendix C</b> Opcode Table                      | 385       |

| <b>Appendix D</b> Instruction Format and Timing     | 397       |

| <b>Appendix E</b> Instruction Disassembly Table     | 433       |

| <b>Appendix F</b> 8086-Family Processor Differences | 441       |

| Index                                               | 445       |

## **Acknowledgments**

A number of people deserve credit for helping make this book a reality. Some I have spoken with and worked with directly; others have worked behind the scenes, doing a wonderful job nonetheless. Working with the people at Microsoft Press was a positive experience, and I sincerely thank them all for their support and encouragement. In addition, my thanks to Ray Duncan for getting the ball rolling, to Intel Corporation for its cooperation, to Matt Trask for his technical review, to my coworkers at Answer Software for their support, and especially to Pam for always believing in me.

This is a book about microprocessor technology, so of course it was written with the assistance of microprocessor technology: I completed a large portion of the manuscript using a Toshiba T1000 portable computer while riding Santa Clara County Transit.

Ross Nelson

June 1988

# INTRODUCTION

The Intel 80386 microprocessor is probably the most widely discussed central processing unit (CPU) chip since the introduction of the 8080 in the early days of personal computing. This book lets you know what all the shouting is about.

After presenting a history of the 8086 microprocessor family in Chapter 1, each subsequent chapter discusses a portion of the 80386 design. The organization of the CPU is presented in Chapter 2. The basic memory architecture is discussed in Chapter 3. Chapter 4 introduces the instruction set of both the 80386 processor and the 80387 numeric coprocessor. Chapter 5 is an explanation of protected-mode operation. Chapter 6 explains how paging extends the memory system. Compatibility with previous processors via real mode, virtual 8086 mode, and the 80286 is covered in Chapter 7. Finally, Chapter 8 provides a full instruction set reference.

This book focuses entirely on programming. It does not discuss the hardware features of the processor unless those features relate to specific instructions. If you are interested in the hardware characteristics of the 80386, refer to the *80386 Data Sheet* and the *80386 Hardware Reference Manual*, both published by Intel Corporation.

To get the most from this book, you should be familiar with computer systems. In particular, an understanding of binary and hexadecimal arithmetic and machine-language programming for some other processor(s) will be helpful.

A large portion of the book is devoted to the 80386's protected mode. Although you do not need to understand this feature to program the 80386, it is important to understand protected mode to grasp why system designers have made the choices they have in implementing the OS/2, Windows/386, PC-MOS/386, and UNIX operating environments.

The conventions throughout this book are summarized on the following pages. If you are familiar with other Intel microprocessors, you are probably already familiar with these concepts.

## Number Formats

I use numbers in three different bases: binary (base 2), decimal (base 10), and hexadecimal (base 16). You can assume that all numbers are base 10 unless they are followed by the suffix "B" (for binary) or "H" (for hexadecimal). For example,

$$1AH = 26 = 00011010B$$

## Data Types

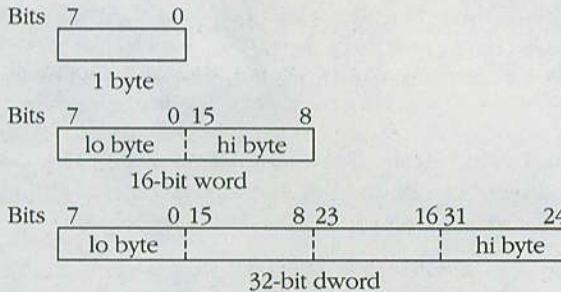

The 80386 can operate on a variety of data types. The most common are 8-bit, 16-bit, and 32-bit quantities. In this book, an 8-bit quantity is called a byte, a 16-bit quantity is called a word, and a 32-bit quantity is called a doubleword, or dword. This nomenclature is unusual because the standard data item size of a computer is commonly called a word. In the Digital Equipment VAX computers, for example, a 32-bit quantity is a word, and a 16-bit quantity is a halfword. The same is true for the Motorola 68000 family and the IBM 370 mainframes.

Although the standard 80386 operand size is 32-bits, Intel retained the naming conventions of its earlier processors because the 80386 is a descendant of the 8086 and the 80286 (16-bit processors). This simplifies running software from the 8086 or the 80286 and lets you use the same assembler to generate code for any of the three processors.

The smallest addressable data item on the 80386 is the byte. All other data items can be broken down into bytes. The 80386 stores larger data items in memory low-order byte first, as the following diagram shows:

Assume that the 32-bit value 100F755DH is stored in memory, beginning at location 10. The individual memory bytes are:

|                  |     |     |     |     |

|------------------|-----|-----|-----|-----|

| <b>Address:</b>  | 10  | 11  | 12  | 13  |

| <b>Contents:</b> | 5DH | 75H | 0FH | 10H |

It is unnecessarily complex, however, to show words and doublewords broken down in byte order, and illustrations in this book treat the quantity as a unit. For example, the book would present the previous value as:

|    |           |   |

|----|-----------|---|

| 31 | 100F755DH | 0 |

|----|-----------|---|

The 80386 can perform operations on items smaller than a single byte, for example, on a single bit or on a bit field. However, the processor always fetches at least one byte from memory when performing these operations.

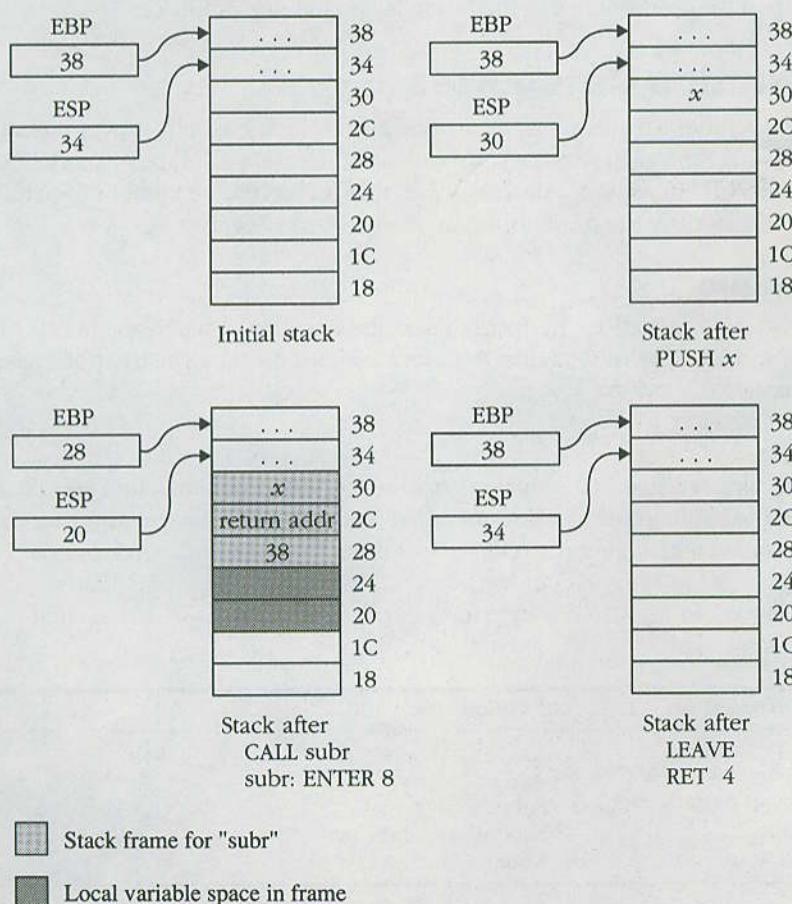

## Assembler Notation

An 80386 instruction is a binary pattern that is decoded by the logic inside the CPU. An instruction can be from 8 to 120 bits in length. Because coding a program using binary patterns would be tedious, programmers use a type of program called an assembler. The simplest type of assembler takes a set of keywords and symbols and translates them into an instruction. The set of keywords and symbols is called the assembler language. Typically, there is a one-to-one mapping between an instruction in assembly language and an actual machine instruction. The assembler would take an instruction such as:

ADD EBX, 5

meaning, “Add 5 to the value in register EBX and store the result in EBX,” and would translate it into the bit pattern:

0001011010101010101010101001111111011111B

The names of the instructions are called mnemonics, and they usually occupy the first field in an instruction line. The subsequent fields are the operands of the instruction and can take a number of forms. The simplest is a numeric value, such as the 5 in the previous example. A register name is another form of operand. An expression within brackets, such as [EBP+2], signifies an operand that is a memory reference.

Throughout the book, I use standard Intel mnemonics. Note, however, that a mnemonic does not necessarily specify the exact encoding of an instruction. For example, the “increment” instruction has a general form in which any operand may be encoded, and the instruction INC EAX would be encoded as FFH 00H. There is also a single-byte instruction for incrementing a general register. In this form, 40H encodes the INC EAX instruction. An assembler will generally choose the most compact form of instruction for any given mnemonic, but the effect of executing either form is the same.

I also use a common convention in discussions about setting bits. I use the term “set” when assigning the value of 1 to a bit, and the term “reset” when assigning the value of 0 to a bit.

## Syntax

This book uses the following syntax:

| <i>Operator</i> | <i>Meaning</i>           |

|-----------------|--------------------------|

| +               | Addition                 |

| -               | Subtraction              |

| ×               | Multiplication           |

| /               | Division                 |

| ~               | Not                      |

| =               | Equal to                 |

| !=              | Not equal to             |

|                 | Or                       |

| ^               | Exclusive OR             |

| &               | Boolean AND              |

| >               | Greater than             |

| <               | Less than                |

| >>              | Shift right              |

| <<              | Shift left               |

| ≤               | Less than or equal to    |

| ≥               | Greater than or equal to |

| ←               | Assignment               |

## 32-bit Instruction Set

The 80386 supports several modes that are compatible with previous Intel processors (the 16-bit 8086 and 80286). However, this book focuses on the 80386's new features and does not discuss the 16-bit architectures of the 8086 and the 80286, even though they are a subset of the 80386's capabilities. Programmers using the 80386 as a replacement for previous processors should be able to do so with reference materials for the 8086 and the 80286.

## Operating System Services

The 80386 implements a complex computer architecture, and it is not reasonable to expect a stand-alone program to take advantage of all the CPU's capabilities. At various times I make statements such as "The operating system will..." or "At this point, the operating system...." In these cases I am not referring to any particular operating system. Instead, I am highlighting a feature of the 80386 that will be implemented by the operating system software and not by an application.

# EVOLUTION OF THE 80386 ARCHITECTURE

Even though I have spent the last eight years working with microcomputers, the phrase "computer system" still brings to mind images of the installation in the basement of the campus library at Montana State University. There, in air-conditioned comfort, behind glass walls, lived Siggie, the university computer system (a Xerox Sigma 7). Housed in several refrigerator-size units, Siggie served the computing needs of the entire university.

Now, the 80386 microprocessor, born of a technology that was first realized while Siggie was still considered state-of-the-art, can serve as the heart of a desktop microcomputer, which has greater computing power than Siggie.

## **The First Components**

The 80386 is the latest member of a line of microprocessors built by Intel Corporation. Intel claims to have invented the microprocessor in 1971, when it was approached by a (now defunct) Japanese corporation to build a custom circuit to serve as the "brains" for a new calculator. Intel designer Ted Hoff proposed that a programmable, general-purpose computing circuit be built instead, and the 4004 became reality. The 4040 and the 8008 chips soon followed, but these chips lacked many characteristics of microprocessors as we know them today.

## **The 8080**

The chip that, by most accounts, led to the birth of the microcomputer industry was the 8080, which Intel introduced in 1974. An article in the September 1975 issue of *Popular Electronics* brought the idea of a "personal" computer to the mass market, and, as they say, the rest is history. The 8080 was the CPU (central processing unit)

in such pioneering systems as the Altair and the IMSAI. Intel did not enjoy a monopoly on the market for long, however; Motorola introduced the 6800, MOS Technology responded with the 6502, and two designers of the 8080 left Intel for Zilog Corporation, which soon produced the Z80. Unlike the 6800 and the 6502, which had completely different architectures, the Z80 was compatible with the 8080 but had an expanded instruction set and ran twice as fast. The battle for CPU supremacy was on.

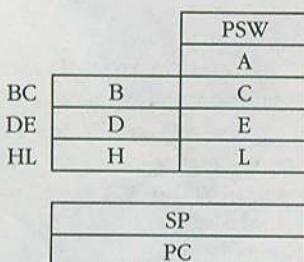

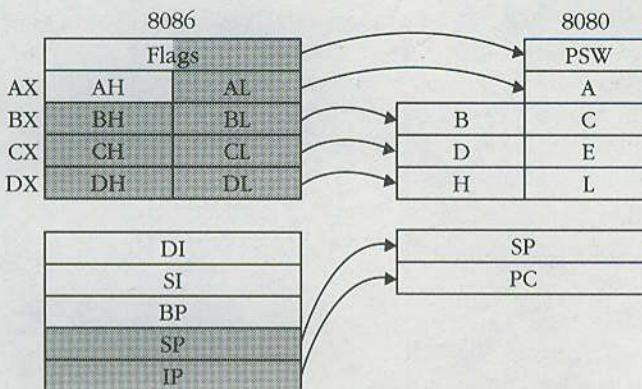

The 8080 was an 8-bit machine; that is, it processed data 8 bits at a time. It had a single accumulator (the A register) and six secondary registers (B, C, D, E, H, and L, shown in Figure 1-1). These six registers could be used in 8-bit arithmetic operations or combined as pairs (BC, HL) to hold 16-bit memory addresses. A 16-bit address allowed the 8080 to access  $2^{16}$ , or 64 KB, of memory.

**Figure 1-1.** The 8080 register set.

Intel also developed a refinement of the 8080 called the 8085, an 8080-compatible processor that featured better performance and a simpler hardware interface.

## The 8086

In 1978, under pressure from other manufacturers' faster, more powerful microprocessors, Intel moved to a 16-bit architecture. The 8086 was touted as the successor to the 8080 microprocessor, and, although the instruction set was new, it retained compatibility with the 8080's instruction set. Figure 1-2 shows how the new registers of the 8086 could be mapped into the set of 8080 registers.

Programs that were written for the 8080 could not be run on the 8086; however, almost every 8086 instruction corresponded to an 8080 instruction. At worst, an 8080 instruction could be simulated by two or three 8086 operations. An Intel translator program could convert 8080 assembler programs into 8086 assembler programs, and the first versions of Microsoft's BASIC and MicroPro's WordStar for the 8086 were ported from 8080 systems via the Intel translator. This concern for compatibility has characterized Intel's presence in the microcomputer market. Every new generation of microprocessor has been able to run software written for the previous generation.

**Figure 1-2.** The 8080-8086 register set map.

In addition to providing software compatibility, Intel was interested in supporting high-level languages. At Intel, almost all programming was done in an Algol-like language called PL/M. Intel believed that a language such as PL/M or Pascal would become the dominant microcomputer development language, so Intel dedicated many 8086 registers to specific purposes, as shown in Figure 1-3.

| Flags |    |                            |

|-------|----|----------------------------|

| AX    | AH | Accumulator                |

| BX    | BH | Base pointer               |

| CX    | CH | Count register             |

| DX    | DH | Data register              |

| DI    |    | Destination index register |

| SI    |    | Source index register      |

| BP    |    | Stack frame base pointer   |

| SP    |    | Stack pointer              |

| IP    |    | Instruction pointer        |

| CS    |    | Code segment               |

| DS    |    | Data segment               |

| SS    |    | Stack segment              |

| ES    |    | Extra segment              |

**Figure 1-3.** The 8086 register set.

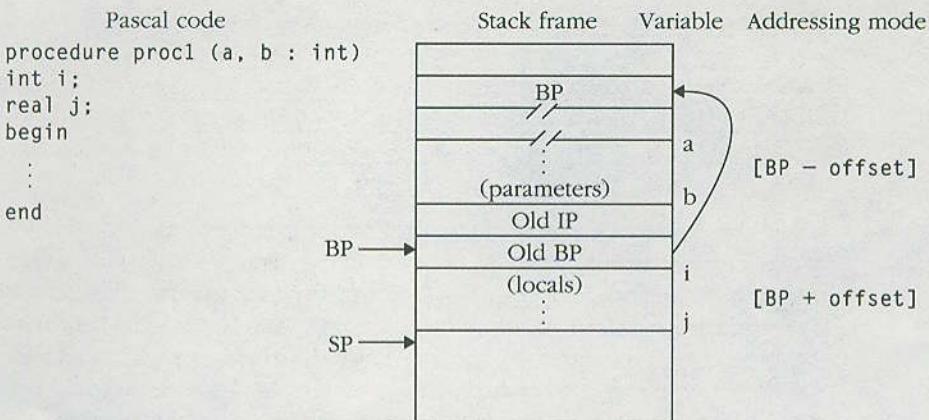

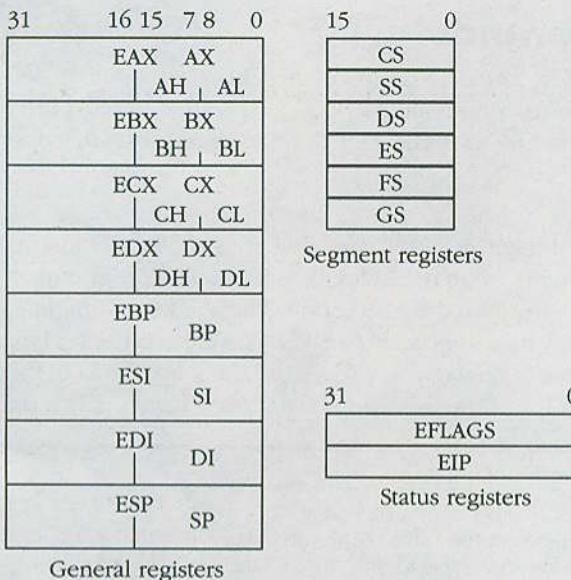

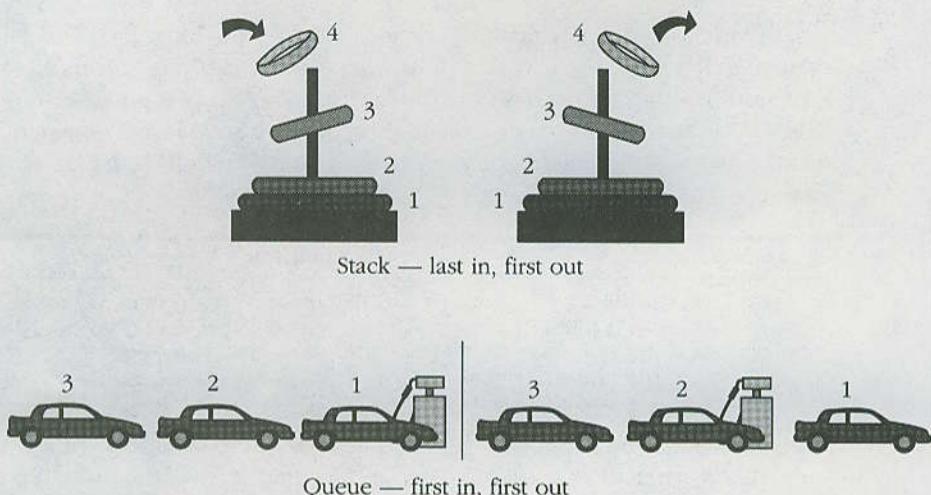

The next two examples show dedicated registers in use. Figure 1-4 shows how high-level languages such as Pascal use the stack pointer (SP) and base pointer (BP) registers.

Figure 1-4. Subroutine context.

In a Pascal program, the context of the currently executing subroutine is maintained on the stack. The values (parameters) provided to the subroutine by the calling routine are first on the stack, then the saved IP of the calling routine, and finally the saved BP of the calling routine. The context also contains stack space for any temporary or local variables that the subroutine uses. Access to either the parameters or local variables is relative to the current value of BP.

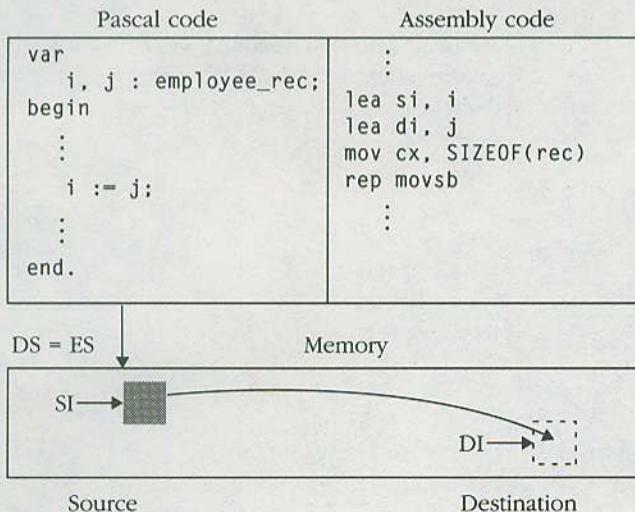

Consider the Pascal assignment statement in Figure 1-5. Because an entire record must be copied, the compiler generates a block move instruction that uses the SI, DI, and CX registers.

Figure 1-5. Block move.

The advantage of dedicating registers is that it allowed Intel to encode the instructions in a compact, memory-efficient manner. The opcode specifies exactly what is to take place; for example, in the MOVS B instruction, specifying the three operands (source, destination, and count) is unnecessary. As a result, the MOVS B opcode is only 1 byte. The disadvantage of dedicated registers is that if you are using SI or DI and want to do a MOVS B instruction, you can't use another register.

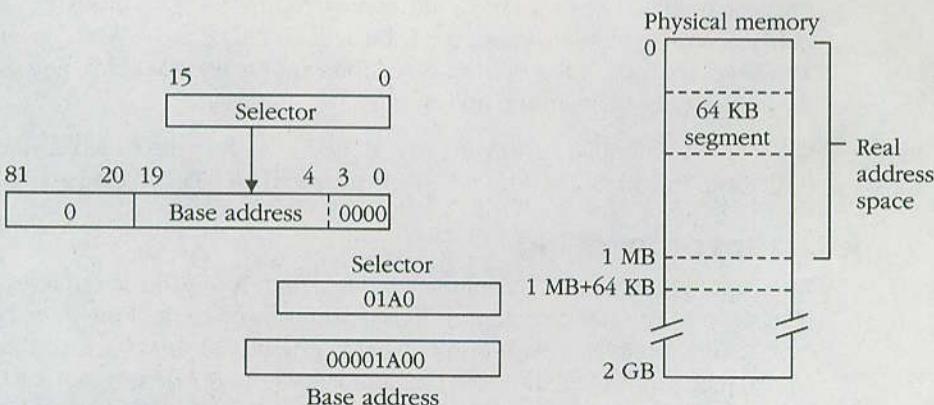

The 8086 also introduced segmentation to the microprocessor world. A segment is a block of memory beginning at a fixed address that is determined by the value in the appropriate segment register. This concept, probably the most despised feature of the 8086 because of the restrictions it imposes, was incorporated for compatibility with the 8080; each segment was 64 KB, equivalent to one 8080 address space. Using segmentation, software can maintain the 16-bit addressing used in the 8080 while expanding (through the use of multiple segments) the memory that the chip can address. The 8086 provides four segment registers that can point anywhere in the 1 MB address space. They are defined as follows:

**CS—The code segment register:** All calls and jumps refer to locations within the code segment.

**DS—The data segment register:** Most memory reference instructions refer to an offset within the data segment.

**SS—The stack segment register:** All PUSH and POP instructions access data in the stack segment. Additionally, any memory reference done relative to the BP register is also directed to the stack segment.

**ES—The extra segment register:** This segment specifies the destination segment in certain string processing instructions.

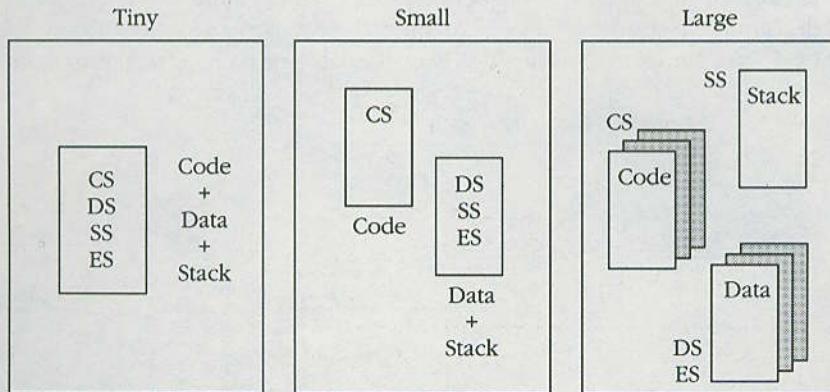

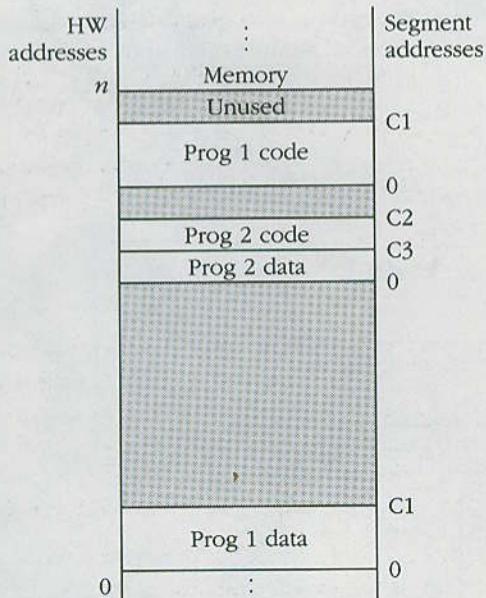

The way an application manages memory (the memory model) is usually consistent throughout a program. When Intel introduced the 8086, three memory models were postulated, which are shown in Figure 1-6.

Figure 1-6. Memory models.

The tiny model mimicked the 8080 address space. The code segment and data segment were in the same area of memory, and the program was limited to 64 KB. The small model was expected to be prevalent because it allowed programs to double in size. By having separate code and data segments, programs could expand to 128 KB and still retain 16-bit addressing. The large memory model allowed the use of multiple code and data segments. In this model, the entire 1 MB address space of the processor could be used.

When the 8086 was introduced in 1978, most microcomputers were limited to 64 KB; almost no one realized how quickly the 64 KB segment limit would become a serious problem. Although the large model allowed programs to fill the entire 1 MB of 8086 address space, using the large model meant using 32-bit pointers. On a 16-bit machine, 32-bit pointers exacted a size and performance penalty that most programmers were unwilling to pay. By the early 1980s, even the 1 MB limit became confining. Additional memory models with names such as "compact" and "medium" were introduced to optimize performance for special programming needs.

Other processors in the 8086 family were the 8088, the 80186, and the 80188. The 8088, introduced a year after the 8086, had the same 16-bit internal architecture but a restricted 8-bit external bus. The 8088 could run the same programs as the 8086, but typically 30 percent slower. The 8088 became wildly successful when IBM chose it for the PC and the PC/XT. The 80186 and 80188 were announced much later, in 1982. These processors kept the same base architecture but included features such as direct memory access (DMA) controllers, on-chip counter/timers, and a simplified hardware interface. They also operated more quickly than did the 8086/8088 and became popular in controller applications.

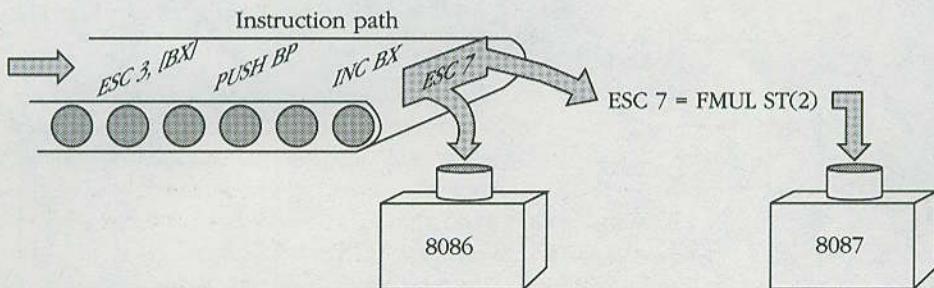

## The 8087

An innovative part of the 8086 family of CPUs is the coprocessor. The ESC or coprocessor escape class of instructions only generated a memory address on the 8086. Additional, special-purpose CPUs could be created to monitor the instruction stream and watch for ESC sequences, as shown in Figure 1-7. Whenever an ESC was detected, the coprocessor could decode the escape as an instruction for itself and perform a function that the 8086 was incapable of doing efficiently on its own.

Figure 1-7. 8086 coprocessor interface.

The first (and only) coprocessor developed for the 8086 was the 8087. The 8087 implemented a floating-point instruction set, capable of as much as 80 bits of precision. Intel worked closely with the IEEE and professors at the University of California, Berkeley, to create a floating-point representation that was flexible and accurate. This representation and its numeric properties have since been formalized as IEEE Standard IEEE-754.

The 8087 contributed to the popularity of the 8086. A desktop computer that contained both an 8086 and an 8087 could do serious scientific work. Implementing floating-point functions in hardware improved the performance of mathematical calculations over existing software routines. However, the 8087 pointed out the problems of the 64 KB segment size. Once scientists and engineers had the computing power to handle real-world problems, they often needed to deal with large arrays of numbers. The 64 KB segment limit restricted a vector of double-precision floating-point numbers to no more than 1024 elements. Software capable of getting around the restriction was soon available, but the "large" memory model was difficult to program in and was slow.

## The 80286

The next major introduction from Intel, the 80286, came in 1982. The 80286 is compatible with the 8086 family, but it also provides a significant performance improvement. It boasts two operating modes: real mode and protected mode. Real mode, which emulates the 8086, is the default mode. The new mode is called protected mode. In protected mode, the 80286 supports the 8086 instruction set but places a new interpretation on the contents of the segment registers that control how memory is accessed.

Although operating systems that are implemented under protected mode are different from those that are designed for real mode, applications can be developed that run in either mode. The design of these dual-mode applications requires that the application observe certain memory restrictions.

Unfortunately, MS-DOS, which is the dominating operating system for 8086-based machines, places no restrictions on how an application addresses memory, and protected mode proved incompatible with a majority of MS-DOS applications. As a result, for a number of years the 80286 was generally treated as a fast 8086 because no one knew how to use protected mode.

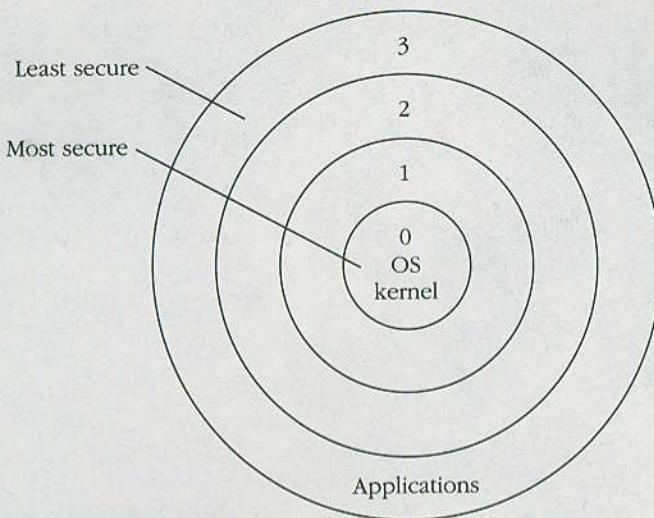

This was unfortunate because the 80286 offered a beneficial new feature—protected mode. Protected mode expands the amount of physically addressable memory from 1 MB to 16 MB, allows the implementation of virtual memory, and provides for the separation of tasks in a multitasking or multiuser environment. Versions of UNIX run in protected mode, but UNIX has not been successful on the 80286 because competitive products usually run on more powerful 32-bit computers. More recently, Microsoft introduced OS/2, which uses almost all protected-mode features.

The 80286 is the first Intel microprocessor designed for “serious” computing. Considerations were made for multitasking, data integrity, and security. The designers examined the architecture of minicomputers and mainframes as they developed the 80286. In addition, two of the main influences on the 80286 designers were the Multics project and a continued belief in Pascal.

Reading the conference papers about the Multics project will enlighten anyone who thinks that protected mode is the product of some Intel designer’s fevered imagination. Multics began in the mid-1960s as a joint research project among MIT, Bell Labs, and General Electric. The project combined hardware and software and was based on the GE 645. The following is a partial list of architectural features that the Multics group pioneered:

- Virtual memory\*

- Protection rings

- Segmented addressing\*

- Descriptor access rights

- Call gates

- Conforming code segments

Some features of Multics also made their way into existing 80286-based software systems. Microsoft’s OS/2, for example, uses dynamic linking, another Multics innovation.

The influence of Pascal on the design of the 80286 is shown by the addition of the ENTER instruction to the 80286 instruction set. The ENTER instruction simplifies creating a stack frame such as the one shown in the subroutine context illustration in Figure 1-4. ENTER can also copy the context or stack frame of the previous subroutine. This ability is not necessary in languages such as FORTRAN or C, but it is useful in languages such as Pascal and Ada that allow nested procedure declarations.

## The 80287

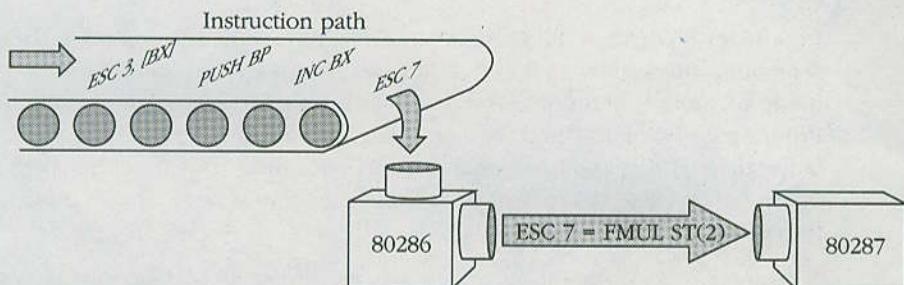

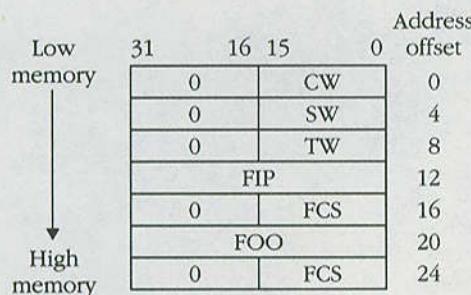

Intel also introduced a new coprocessor for the 80286, but the 80287 was a bit of a disappointment. Although the 80286 executes programs two to three times faster than the 8086, the performance of the 80287 is about the same as the 8087. Intel did not really modify the computational engine of the 8087 in creating the 80287, so the new coprocessor does not run any faster. Intel did change the interface between the CPU and the coprocessor, however, eliminating the need for the coprocessor to monitor the instruction stream of the main CPU.

In this new interface method, illustrated in Figure 1-8, the main CPU decodes the ESC instructions and then passes the information to the coprocessor via the I/O

---

\*The Multics group did not invent these features, but they were an integral part of the system.

channel. Because addressing is treated differently in real mode than it is in protected mode, the coprocessor would have had to operate in different modes as well, using the old interface method. Instead, the new interface requires the 80286 to validate all addresses before signaling the 80287. This interface allows the coprocessor to run at a clock rate different from that of the main CPU, and it also allows the 80287 to be used with CPUs other than the 80286.

Figure 1-8. 80286 coprocessor interface.

## Competitive Pressures

Between the introduction of the 8086 and the 80286, Motorola developed what became the strongest competition to Intel's dominance of the microprocessor market, the 68000 family. Several features of the Motorola microprocessors were attractive to the development community. The 68000 family incorporates a 32-bit internal register file for data and addressing. This allows a large application address space without the limitation of 64 KB segments. This 32-bit capability also makes it easy to port operating systems (such as UNIX) and minicomputer applications to the 68000-family processors.

Motorola also boasted about the "orthogonality" of the 68000 instruction set. Unlike the 8086 and the 80286, with their special-purpose registers, the 68000 allowed programmers to specify any register for a given instruction. Although all 68000 microprocessors had 32-bit register files, the first two CPUs (68000 and 68010) were limited to 24-bit addresses and a 16-bit memory interface. In 1985, however, Motorola began sampling the 68020, which had a full 32-bit address bus and a 32-bit data bus. Although Intel had most of the business microcomputer market, makers of scientific and engineering workstations almost unanimously chose Motorola CPUs for their products.

## Intel's 32-Bit Microprocessor

Intel's design engineers faced two problems: compatibility and performance. They needed to maintain compatibility with the previous generation of processors to retain their share of the PC business market; Intel's marketing force frequently referred to the "billions and billions" of bytes of code (applications) that the 80386

had to be able to run. At the same time, they needed a product that would address the shortcomings of the 8086 family architecture, which gave Motorola an edge in scientific and engineering markets. The resulting product, the 80386, addresses these issues by operating in a number of modes. At boot time, it operates in real mode like the 80286 and is nothing more than a very fast 8086. It uses 16-bit registers and the 8086 segmentation scheme, and it is subject to the 1 MB memory limitation.

But the 80386 can also be switched to protected mode. In protected mode, each segment is marked by a bit that designates whether the segment is a protected-mode segment containing 16-bit 80286 code or a 32-bit protected-mode segment. Programs residing in 32-bit segments can use the extended address space (segments larger than 64 KB) and additional features, including array indexing, orthogonal use of the register set, and special debugging capabilities not found in previous processors.

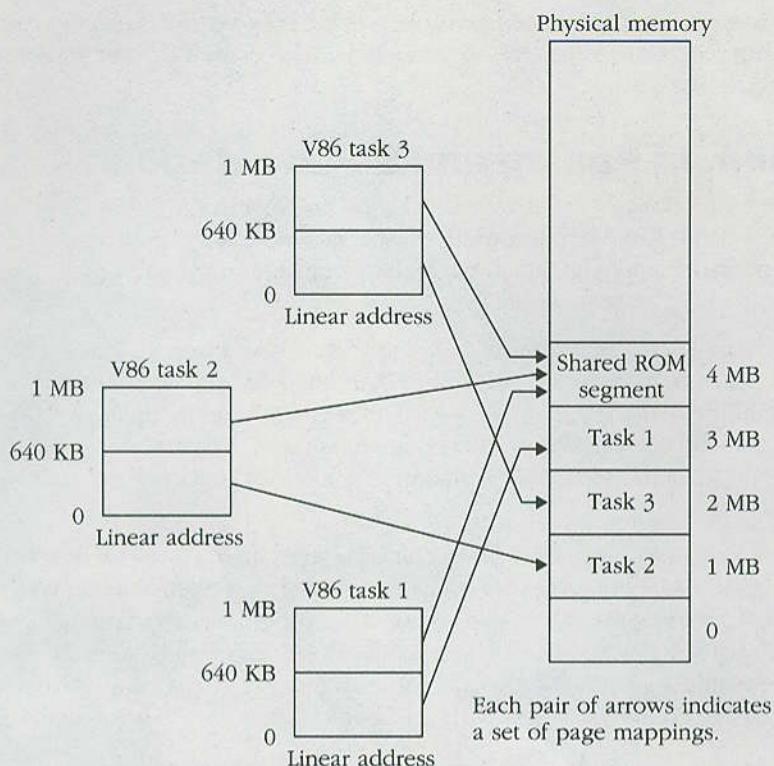

A protected-mode operating system can also create a task that runs in virtual 8086 mode. An application running in this mode believes that it is running in real mode or on an 8086. However, the operating system can designate certain classes of input/output (I/O) operations that it will not allow. If the application attempts to violate any operating system rules, an interrupt is generated that transfers control from the application to the operating system. By examining the instruction that the application was trying to execute, the operating system can choose to block the application from running, simulate the operation, or ignore it and let the application continue. The operating system also maps the 1 MB 8086 address space that the application believes it is running under to the actual memory space that the operating system wants the application to use. A protected-mode operating system can establish multiple virtual 8086 tasks.

The 80386 also extends the similarities between the Intel architecture and the Multics system. Like Multics, the 80386 integrates the ability to perform demand paging (a virtual-memory technique used in minicomputers and mainframes) with segmentation.

## **The 80387**

The most recent microprocessor line from Intel also boasts a new coprocessor, the 80387. The interface between the CPU and the coprocessor is the same one defined for the 80286 and the 80287. The 80386 can be coupled with the 80287 to provide a lower-cost floating-point environment. The 80387 provides a significant performance improvement over its predecessor, executing floating-point benchmarks about five times faster.

## **80386 Family Extensions**

Intel has indicated that the 80386 product line will continue to evolve. The next generation processor will be called the 80486 and will include capabilities beyond those of the 80386. However, Intel has committed to broadening support for the

80386 as well. Intel recently introduced the 80386SX and the 80387SX, which are fully compatible with the 80386/80387 but support only a 16-bit external data bus and a 24-bit external address bus. Intel plans to introduce other processors that use the 80386 native mode instruction set but that do not support compatibility features such as real mode or V86 mode.

## Summary

As you can see from the following table, the 80386 technology has significantly advanced beyond that of its predecessors; however, the road to 32-bit computing was not necessarily straight and narrow. The 80386 has been shaped by a number of forces: the ideals of the designers, the limits of compatibility (some stemming from the early days of the 8080), threats from the competition (both real and perceived), and other factors such as Pascal, Multics, and UNIX. Now that I've shown the origins of the 80386, the remainder of the book will show what the 80386 is and what it does.

**Relative Performance**

|                              | <b>8086/87</b> | <b>80286/287</b> | <b>80386/387</b> |

|------------------------------|----------------|------------------|------------------|

| <b><i>Integer</i></b>        | 1.0            | 2.7              | 6.7              |

| <b><i>Floating point</i></b> | 1.0            | 1.7              | 10.0             |

If the 8086/87 performance is 1.0, the 80386/387 is approximately 6.7 times faster performing integer calculations and approximately 10 times faster performing floating-point calculations.

# THE 80386 ARCHITECTURE

Back in 1837, when Charles Babbage was musing over the idea of computation automata, he referred to his grandest scheme as an "analytical engine." At that time, especially considering the mechanical aspects of Babbage's idea, an engine was an apt metaphor for a computing device: fuel, combustion, and power *vs* input, computation, and output.

## A Data-Processing Factory

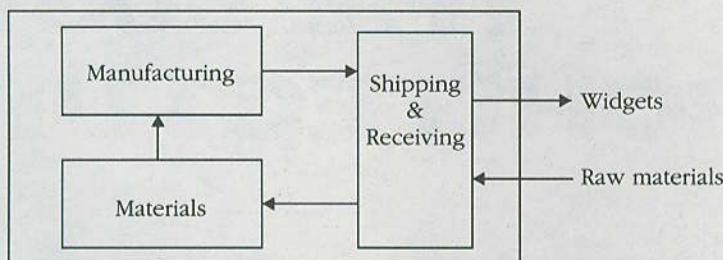

In recent years, however, this machinelike cycle led to limitations on the amount of work that could be accomplished. A modern microprocessor such as the 80386 might be more successfully compared with a factory than with an engine. At the heart of this data-processing factory, the computational engine remains, but it is surrounded by a bevy of supporting departments.

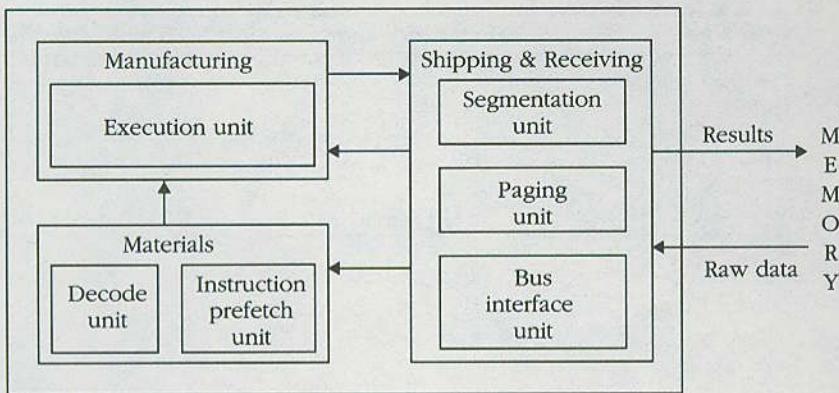

Figure 2-1 on the following page illustrates our imaginary widget factory. It is composed of three departments: Shipping and Receiving, Materials, and Manufacturing. The Shipping and Receiving department deals with the world outside the factory. It orders truckloads of raw materials from suppliers and passes them to the Materials department. The goods are sorted here and warehoused until needed. The Manufacturing department, the "engine" of the factory, forges the finished widgets from the raw materials and routes them to Shipping and Receiving, where they are sent to the outside world.

The efficiency of this model lies in the parallel nature of the different activities. At the same time as the Materials department requests the raw goods necessary to build widgets, Manufacturing builds the current supply of widgets, and Shipping and Receiving deals with the outside world, buys unfinished goods, and ships the newly finished widgets.

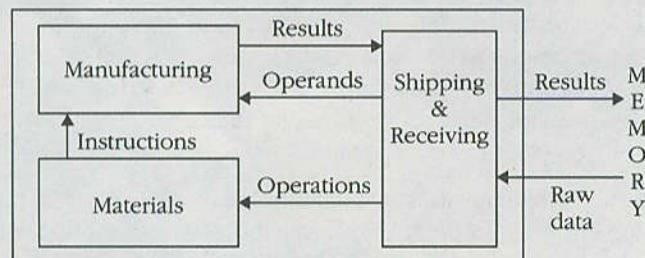

Conventional computers receive two classes of data: instructions and operands. The instructions tell the computer which operations to perform on the operands.

Similar to the operation of our imaginary factory, the 80386 can work on more than one instruction simultaneously. In the jargon of the computer industry, this is called *pipelining*.

**Figure 2-1.** Widget factory.

In Figure 2-2, I recast the widget factory as a data-processing factory analogous to the operation of the 80386. The Shipping and Receiving department pulls in bytes of data from memory. Instructions then move to the Materials department, where they are decoded and stored. When requested, the new instructions and any necessary operands pass to the Manufacturing department, the computational engine. The results of an operation pass back to Shipping and Receiving, which stores the results outside the CPU, in memory.

**Figure 2-2.** Data-processing factory.

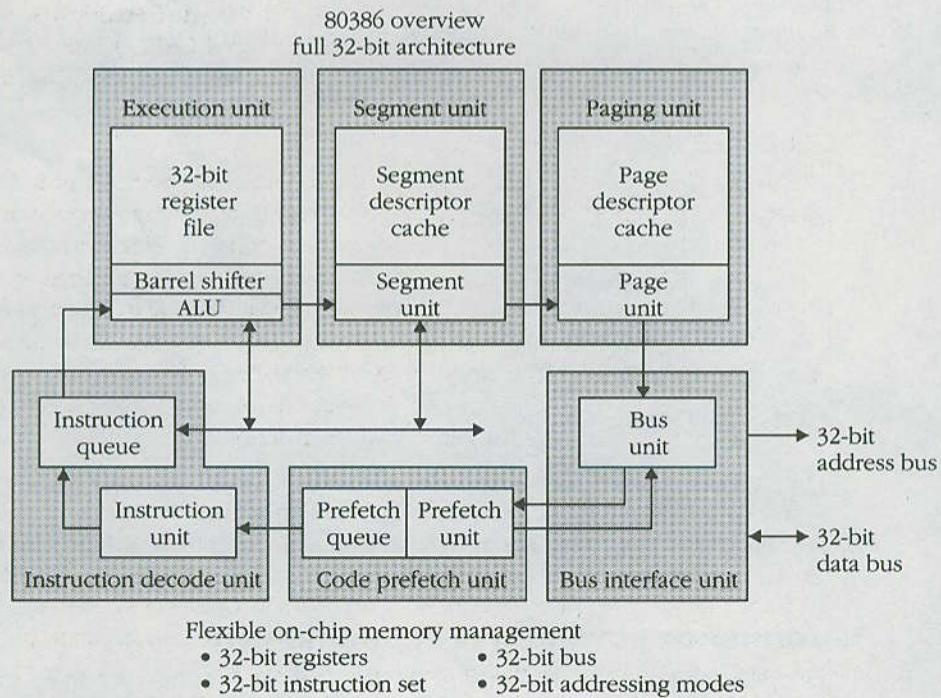

Although simple, this picture of the flow of information through the 80386 is fairly accurate. The three departments in the example correspond to six logical units in the 80386, as shown in Figure 2-3. Each unit operates in parallel with the other units. Later sections of this chapter describe the operation of each unit.

Figure 2-3. 80386 factory.

### Keeping the factory moving

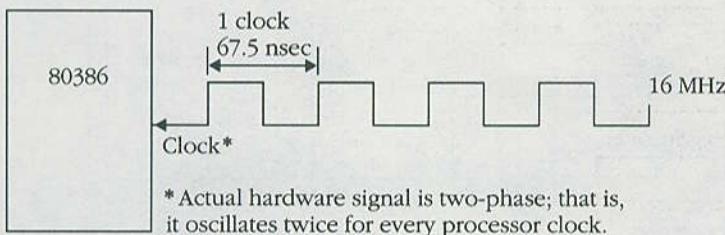

The 80386 runs to a heartbeat called the clock signal. This regular electronic pulse keeps all units of the 80386 synchronized. The clock signal is a square wave oscillating at a specific frequency, as shown in Figure 2-4. Instruction timings, memory access times, and operational delays are measured in terms of clocks, or one complete square-wave cycle. A typical frequency for an 80386-based system is 16 MHz. At 16 MHz, one clock is 62.5 nanoseconds.

Figure 2-4. A square-wave cycle.

The timings of each processing unit are also measured in clocks. The shortest possible execution time is  $\frac{1}{2}$  clock. This is possible because the square-wave input to the 80386 CPU chip oscillates at twice the clock frequency, making a two-phase clock.

### Performance advantages of parallelism

The pipelined operation of the 80386 "hides" portions of instruction execution time. Some operations necessary to execute an instruction occur during the previous instruction. The table that follows illustrates the difference between executing a typical instruction (ADD ECX, [EBP+8]) on the 80386 and executing it on a similar, imaginary processor without pipelining.

| Operation             | With Pipelining | Without Pipelining |

|-----------------------|-----------------|--------------------|

| Instruction fetch     | 0 clocks        | 2-4 clocks         |

| Instruction decode    | 0 clocks        | 1 clock            |

| Operand address xlate | 0-6 clocks      | 2-8 clocks         |

| Operand read          | 3 clocks        | 3 clocks           |

| Execute               | 2 clocks        | 2 clocks           |

| Total:                | 5-11 clocks     | 10-18 clocks       |

Pipelining lets the 80386 execute an instruction about twice as quickly as a similar processor that performs each step of the instruction sequentially. Some instructions that have no operands appear to execute in "zero" time because of the parallel nature of 80386 operating units.

## 80386 Microarchitecture

Figure 2-5\* shows a block diagram of the internal operating units of the 80386. Although the programmer sees the 80386 as a single entity, it is instructive to see how the 80386 achieves the division of labor that contributes to its speed.

Figure 2-5. 80386 microarchitecture.

\* Reprinted by permission of Intel Corporation, copyright 1986.

## Bus interface unit

The bus interface unit (BIU) is the 80386's gateway to the external world. Any other unit that needs data from the outside asks the BIU to perform the operation. Similarly, when an instruction needs to write data to memory or to the I/O channel, the BIU is presented with the data and address and is asked to place it on the bus. The bus interface unit deals with physical (hardware) addresses only, so operand addresses must first pass through the segmentation unit and the paging unit, if necessary.

## Instruction prefetch unit

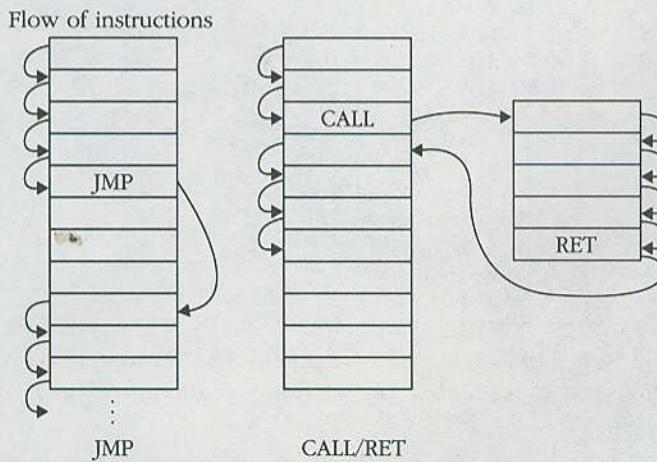

The job of the prefetch unit is relatively simple. The instruction decode unit empties a 16-byte queue, and the prefetch unit tries to keep the queue full. The prefetch unit continually asks the BIU to fetch the contents of memory at the next instruction address. As soon as the prefetch unit receives the data, it places it in the queue and, if the queue is not full, requests another 32-bit piece of memory. The BIU treats requests from the prefetch unit as slightly less important than requests from other units. In this way, currently executing instructions requesting operands receive the highest priority and are not slowed down, but prefetches still occur as frequently as possible. The prefetch unit is notified whenever the execution unit processes a CALL, a JMP, or an interrupt so that it can begin fetching instructions from the new address. The queue is flushed whenever a CALL, a JMP, or an interrupt occurs, which prevents the execution unit from receiving invalid instructions.

## Instruction decode unit

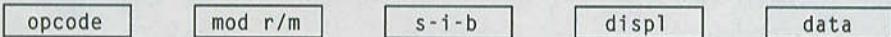

The instruction decode unit has a job similar to that of the prefetch unit. It takes individual bytes from the prefetch queue and determines the number of bytes needed to complete the next instruction. A single instruction in the 80386 can be anywhere from 1 to 16 bytes. After pulling the entire instruction from the prefetch queue, the instruction decode unit reformats the opcode into an internal instruction format and places the decoded instruction into the instruction queue, which is three operations deep. The instruction decode unit also signals the BIU if the instruction just decoded will cause a memory reference. This allows the operands of the instructions to be obtained prior to the execution of the instructions.

## Execution unit

The execution unit is the part of the CPU that does computations. It performs any shifts, additions, multiplications, and so on that are necessary to accomplish an instruction. The register set is contained inside the execution unit. The unit also contains a logic component called a barrel shifter, which can perform multiple-bit shifts in a single clock cycle. The execution unit uses this capability not only in shift instructions but in accelerating multiplications and in generating indexed addresses. The execution unit also tells the bus interface unit when it has data that needs to be sent to the memory or I/O bus.

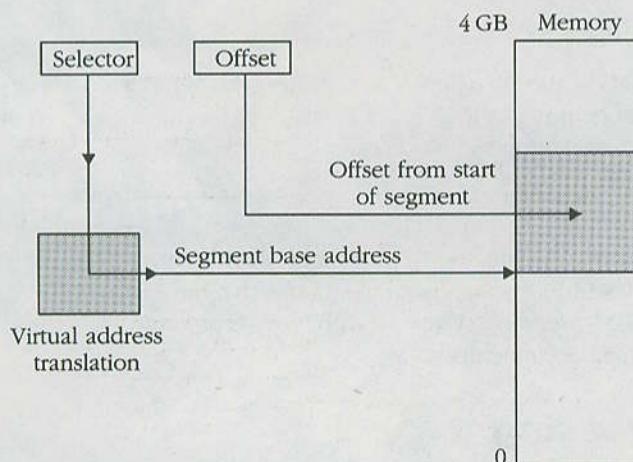

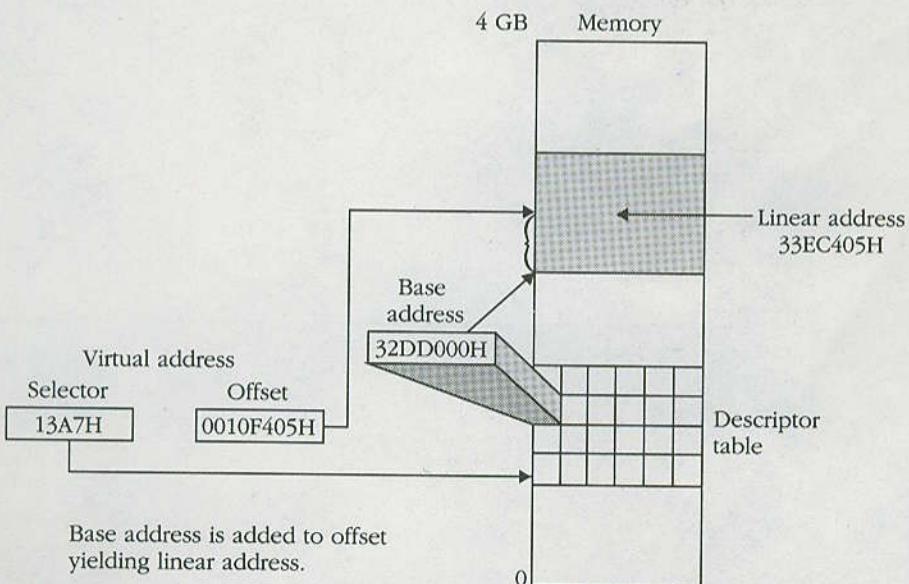

## Segmentation unit

The segmentation unit translates segmented addresses into linear addresses. Segment translation time is almost entirely hidden by the parallelism of the 80386. At the most, one clock is required to complete the address translation. The typical case is zero clocks. The segmentation unit contains a cache that holds descriptor table information for each of the six segment registers. This unit is described further in Chapter 3.

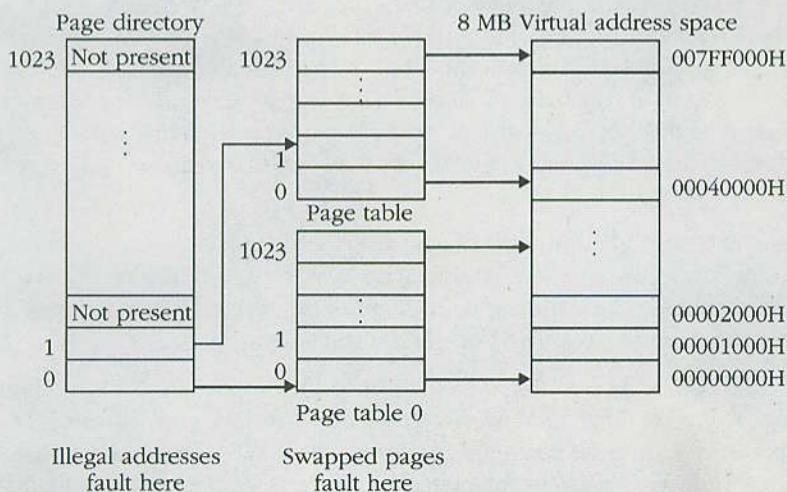

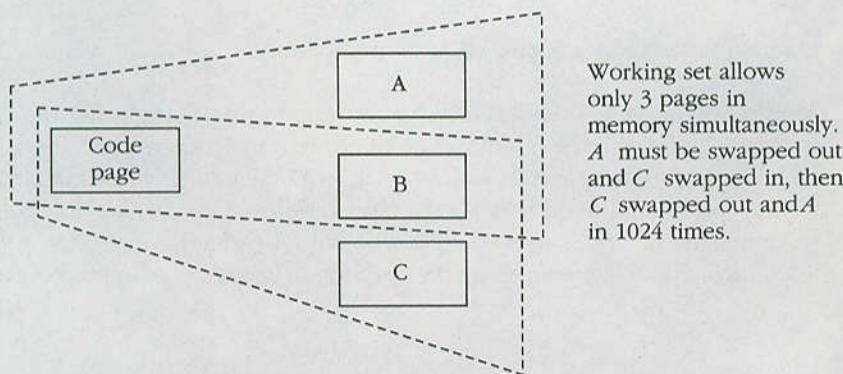

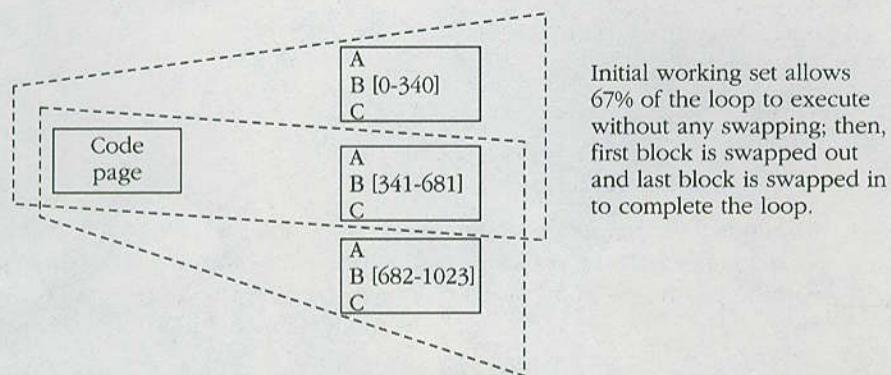

## Paging unit

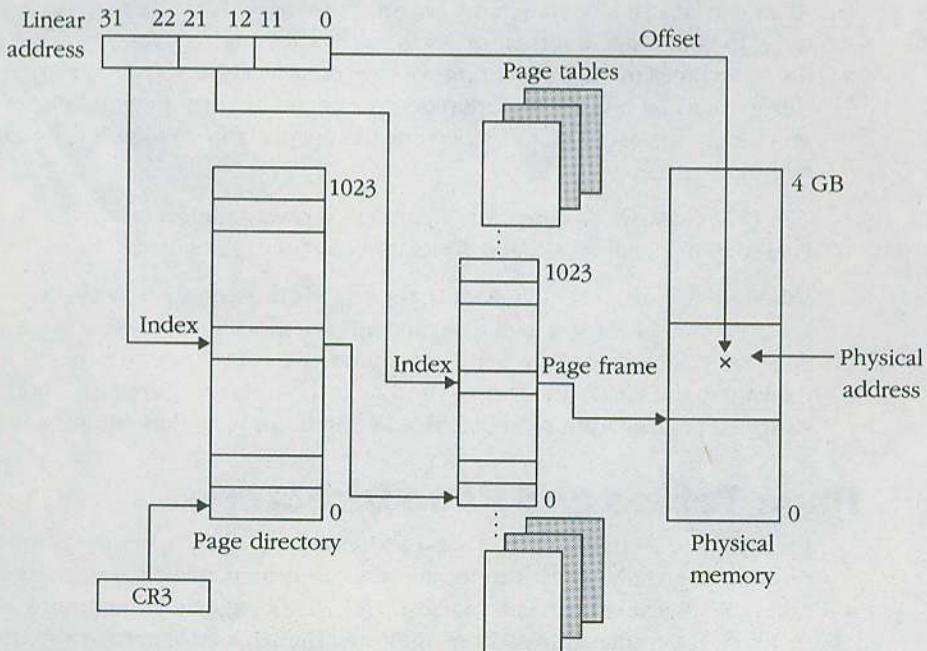

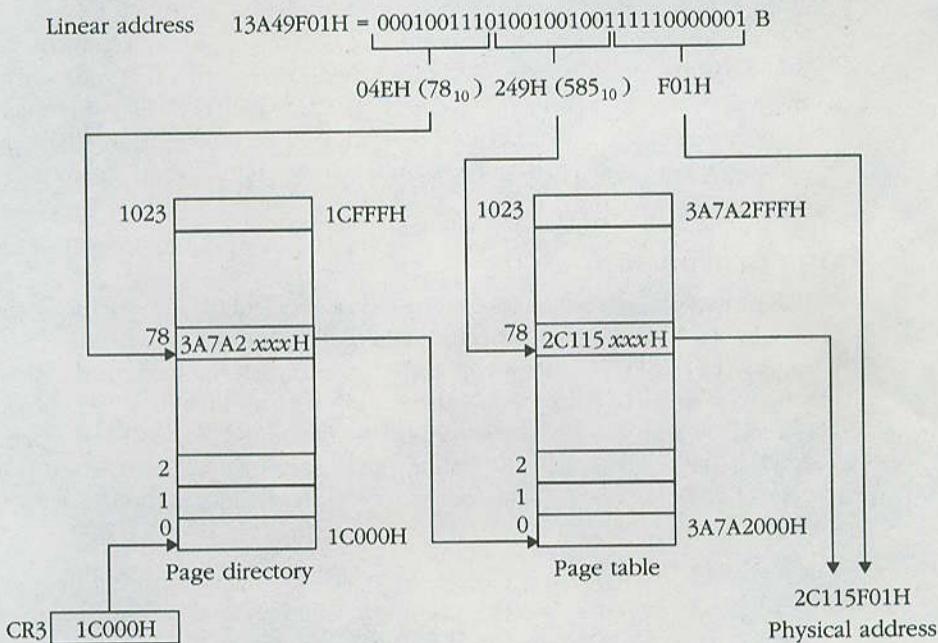

The paging unit takes the linear addresses generated by the segmentation unit and converts them to physical addresses. If paging is disabled, the linear addresses of the segmentation unit become the physical addresses. When paging is enabled, the linear address space of the 80386 is divided into 4096-byte blocks called pages. Each page can be mapped into an entirely different physical address. Chapter 6 discusses the paging process in detail.

The 80386 microprocessor uses a page table to translate every linear address to a physical address. The paging unit contains an associative cache called the translation lookaside buffer (TLB), which contains the entries (new addresses) for the 32 most recently used pages. If a page table entry is not found in the TLB, a 32-bit memory read cycle fetches the entry from RAM. Under typical operating conditions, less than 2 percent of all memory references require the 80386 to look outside the TLB for a page table entry.

The time required to perform the translation varies between 0 and 5 clocks. Thanks to the TLB, the typical delay is only  $\frac{1}{2}$  clock.

## Instruction Set Architecture

The execution unit presents the programmer with the model for instruction execution. It contains the logic to process instructions, to operate on various data types, and to interpret control information.

Because the 80386 is a 32-bit machine, the typical size of an 80386 operand is a 32-bit quantity. Also, because the 80386 processes data 32 bits at a time, it is said to have a *word size* of 32 bits. Unfortunately, the term "word" is ambiguous when referring to the 80386.

For compatibility, *word* refers to a 16-bit quantity, as it did in the 8086 and 80286 environments. The term *dword*, or *32-bit word*, refers to a 32-bit quantity.

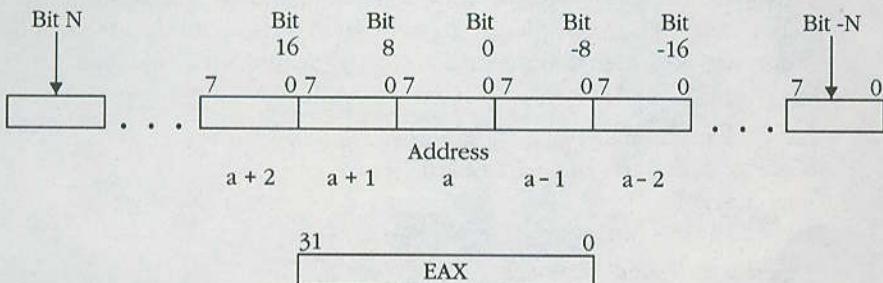

## Bits and bit strings

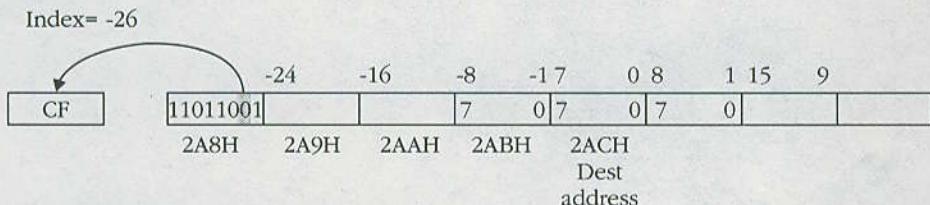

Although the basic (default) operand size on the 80386 is 32 bits, it can manipulate quantities of various sizes. The most elementary is the bit. A bit is a single binary digit, and the 80386 implements a number of instructions that test and modify individual bits. Bits are addressed as an offset from a register or memory location. The

low-order bit of the operand is designated as bit 0, the high-order bit in the low-order byte is bit 7, and the low-order bit of the next byte is bit 8. Figure 2-6 shows the bits in a register and in memory. If the operand resides in memory, negative bit offsets can also be used. Bit  $-1$  is the high-order bit of the byte immediately preceding the memory address.

Figure 2-6. Bit strings.

## Bytes

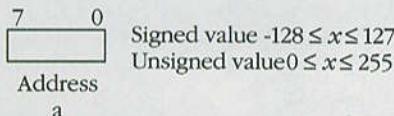

The byte is the basic unit of addressability on the 80386; that is, address 3 refers to the third byte in memory, not the third dword. A byte is an 8-bit quantity that can be interpreted as either a signed or an unsigned value. Figure 2-7 shows the layout of a byte and the range of values that it can specify.

Figure 2-7. Byte value range.

When a byte is interpreted as an unsigned number, it can take on a value ranging from 0 through 255. If a byte is interpreted as a signed number, it is assumed to be in *two's complement* notation. This notation allows a single byte to store values ranging from  $-128$  through  $+127$ . To determine the value of a two's complement number, follow these steps:

1. Examine the most significant bit (MSB) of the value. If the MSB is 0, the number is positive and can be read as if it were an unsigned value. If the MSB is 1, the value is negative.

2. You can find the absolute value of the number by taking the *complement* of the number (inverting the value of each bit) and adding 1.

For example, consider the binary value 10111100B. The most significant bit, 1, indicates that the number is negative. To find the absolute value, take the complement

(01000011B) and add 1. The result, 01000100B, is 68 decimal, so 10111100B represents the value -68.

## Words

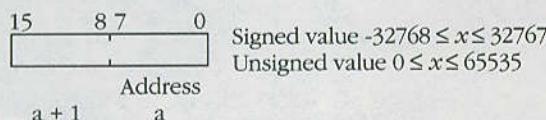

Words, as previously defined, are 16-bit quantities. Figure 2-8 shows the range of values that can be stored in a word. When a word is written to memory, it is stored in two bytes. The low-order byte is written to the specified address, and the high-order byte is written to the next consecutive memory location.

Figure 2-8. Word value range.

Word values are interpreted as signed or unsigned in the same way as are byte values. The only differences are that bit 15 is the MSB and that there is a greater range of possible values.

## Dwords

Dwords are 32-bit quantities. Like bytes and words, they can be signed or unsigned. The extra bits allow representation of integral values greater than 2 billion. Figure 2-9 illustrates the range of values for dwords and the way they are stored in memory. Like words, dwords are stored in memory low-order byte first. If the low-order byte is stored at address  $m$ , the high-order byte is stored at address  $m + 3$ .

Figure 2-9. Dword value range.

The computer industry does not agree on the proper method of breaking up large values into bytes for memory storage. Computers like the DEC VAX use the same technique as the 80386. Others, such as the IBM 370 or the Motorola 68020, store the high-order byte first. This can be a consideration when porting programs from one computer to another.

## Quadwords

Quadwords are 64-bit numeric quantities. No instructions reference quadword memory operands. However, the 32-bit Multiply instruction generates a 64-bit value, with the high-order bits in register EDX and the low-order bits in register EAX. Conversely, the Divide instruction accepts a 64-bit dividend stored in the same register format. Storing a quadword in memory requires two MOV instructions.

## ASCII and BCD

In the previous examples, the values discussed represent numbers. For ASCII and BCD, the binary patterns represent encodings of information. ASCII stands for American Standard Code for Information Interchange. ASCII values are 7 bits of information stored in a single byte. The most significant bit is 0. A particular bit pattern represents a predefined value. For example, the binary pattern 0101011B represents the plus character (+). 1010011B represents the letter S, and 0110101 represents the digit 5. Appendix B contains a table of all ASCII characters.

Similarly, BCD, which stands for binary coded decimal, encodes representations of decimal numbers in a binary format. Encoding a decimal digit requires 4 bits. Because using only 4 bits of a byte is inefficient, 2 BCD digits are often stored in a single byte. This representation is called *packed BCD*. Figure 2-10 shows how values are stored in BCD notation.

| BCD  | Decimal | 1     | 7     | 9     | 3     | 2    | BCD     |

|------|---------|-------|-------|-------|-------|------|---------|

| 0000 | 0       | 0001  | 0111  | 1001  | 0011  | 0010 |         |

| 0001 | 1       |       |       |       |       |      | Address |

| 0010 | 2       | a + 4 | a + 3 | a + 2 | a + 1 | a    |         |

| 0011 | 3       |       |       |       |       |      |         |

| 0100 | 4       |       |       |       |       |      |         |

| 0101 | 5       |       | 1     | 7     | 9     | 3    |         |

| 0110 | 6       | 0000  | 0001  | 0111  | 1001  | 0011 | Packed  |

| 0111 | 7       |       |       |       |       |      | BCD     |

| 1000 | 8       |       |       |       |       |      | Address |

| 1001 | 9       |       | a + 2 |       | a + 1 |      |         |

| 1010 |         |       |       |       |       | a    |         |

| ⋮    |         |       |       |       |       |      |         |

| 1111 |         |       |       |       |       |      |         |

} Invalid

Figure 2-10. BCD storage.

Because ASCII and BCD provide ways to encode numeric values and do not have a fixed length, they can be used to implement variable-precision numbers. The 80386 supports ASCII and BCD arithmetic via the Decimal Adjust and ASCII Adjust instructions. Chapter 4 discusses ASCII and BCD arithmetic.

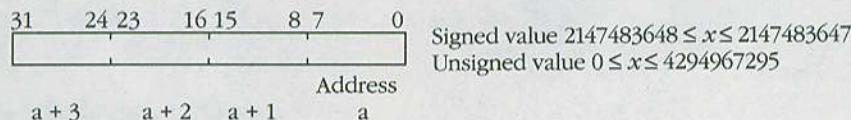

## The 80386 Register Set

In addition to implementing the logic to execute instructions, the 80386 has a number of storage locations on the chip, called *registers*. Because they are inside the CPU, registers can be accessed as operands much more rapidly than can external memory. The general registers are used by the 80386 to store frequently accessed operands. Other registers contain special values that control specific aspects of 80386 operation.

The 80386 register set is partitioned into five classes: the *general registers*, which applications use for data storage and computation; *segment registers*, which affect memory addressing; *protection registers*, which help support the operating system; *control registers*, which modify the behavior of the processor; and *debug and test registers*, which are used as their name implies.

## General registers

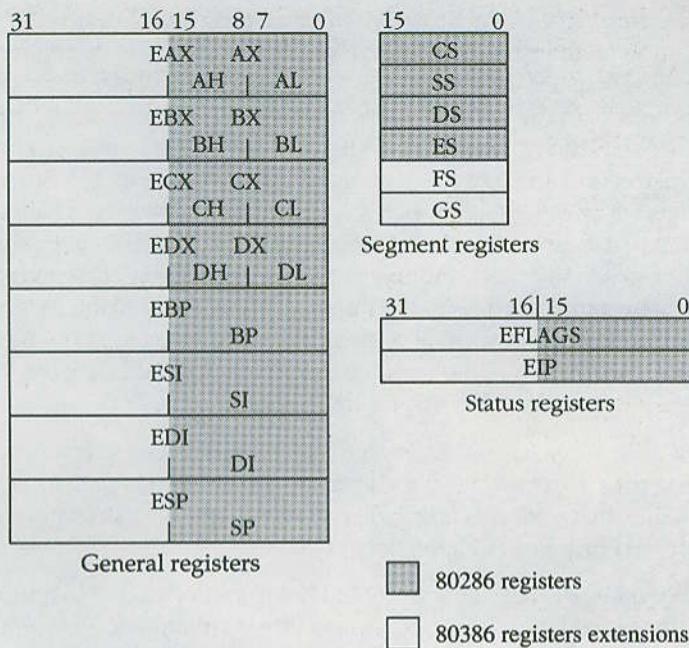

The general registers are named EAX, EBX, ECX, EDX, ESI, EDI, EBP, and ESP, as shown in Figure 2-11. As a rule, any instruction can use any general register except ESP, either as an operand or as a pointer to an operand in memory. Exceptions are noted in Chapter 4 in the discussion of the instruction set.

Figure 2-11. 80386 base register set.

In the 80386, you can address selected portions of these registers. The part of the register accessed depends on whether you are performing an 8-bit, 16-bit, or 32-bit operation. Each division of a register has a separate name. For example, EAX is the name of one of the 32-bit registers. The lower 16 bits are addressable as AX, and that half of the register is accessible as AL (the low-order 8 bits) or AH (the high-order 8 bits). These names are left over from previous generation microprocessors, the 8080 and 8086, as discussed in Chapter 1. The 80386 extends the 80286 register set to 32 bits, similar to the way that the 8086 and 80286 extended the 8-bit registers of the 8080 to 16 bits. Figure 2-12 shows a map of the register extensions.

Figure 2-12. 386/286 registers.

Two additional registers hold status information about the current instruction stream. The EIP register contains the address of the currently executing instruction, and the EFLAGS register contains a number of fields relevant to different instructions.

Like the other registers, EIP and EFLAGS have 16-bit components, IP and FLAGS. The 16-bit forms of these registers are used in virtual 8086 mode and in running code written for the 80286.

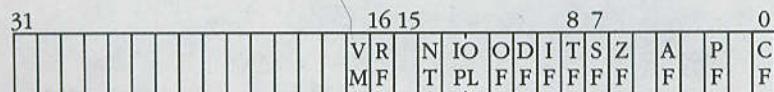

### EFLAGS register

A breakdown of the EFLAGS register looks like this:

**VM—Virtual 8086 mode:** When this bit is set, it indicates that the currently executing instruction stream is 8086 code. The implications of virtual 8086 mode are covered in Chapter 7. Applications cannot change the VM (virtual machine) bit, and instructions that modify EFLAGS leave the VM bit unchanged. Only the task-switch operation or an interrupt/interrupt return can alter the VM bit.

**RF—Resume flag:** This bit controls whether a debug fault can be generated during the execution of an instruction. When an exception occurs during program execution, the 80386 pushes the current CS, EIP, and EFLAGS registers onto the stack and transfers control to the proper exception handler. The stack image of the EFLAGS register has the RF bit set to 1. When the exception handler returns to the interrupted instruction, the RF bit is on, and the 80386 prevents a debug fault from being generated. Any other faults (such as page faults or protection faults) occur as usual. The debug exception has the highest priority of all 80386 exceptions; if, therefore, an instruction causes multiple faults, the first one processed is the debug exception. When control returns to the interrupted instruction, the RF bit is set, and the instruction is completed without retriggering the debug fault. The 80386 clears the RF bit upon completion of the interrupted instruction. (See Chapter 5 for a discussion of exceptions and support for debugging.)

**NT—Nested task flag:** The 80386 sets this bit whenever a CALL, interrupt, trap, or exception causes a task switch. The bit is set in the EFLAGS register of the new task and indicates that a reverse task switch (IRET) is valid. Task switching in the 80386 is discussed further in Chapter 5.

**IOPL—I/O privilege level:** This 2-bit field holds a value of 0–3 that indicates the privilege level required to perform I/O instructions. Although IOPL is in the EFLAGS register, no procedure can modify it unless the procedure is running at privilege level 0, and then only by using the POPF instruction.

A procedure's current privilege level (CPL) must be equal to or more privileged than the IOPL to execute any of the following instructions: IN, INS, OUT, OUTS, CLI, or STI. A procedure that can execute these instructions is said to have *I/O privilege*.

**OF—Overflow flag:** When an arithmetic integer instruction is executed, the OF bit is set if the result is too large or too small to fit in the destination register or memory address. Because the OF flag is set relative to integer instructions, the 80386 presumes that the destination register is one bit smaller in size to allow for the sign bit. The following instructions illustrate some examples.

|                |                                       |

|----------------|---------------------------------------|

| MOV AL, 127    | ; AL = 7FH, largest 8-bit             |

|                | ; signed integer OF = 0               |

| ADD AL, 2      | ; result, AL = 81H (-127)             |

|                | ; should be AX = 0081 (129), OF = 1   |

| MOV CX, -35000 | ; CX = 7748H, OF = 0                  |

| SUB CX, 7002   | ; result, CX = SBEEH (42002)          |

|                | ; should be ECX = FFFF5BEEH (-42002), |

|                | ; OF = 1                              |

Note that the OF bit is ignored if unsigned arithmetic is intended. For example, adding 127 and 2 in register AL generates a valid, unsigned result of 129.

**DF—Direction flag:** The direction flag bit modifies the behavior of the string instructions: MOVS, STOS, LODS, CMPS, SCAS, INS, and OUTS. When DF is 0, the string instructions operate on incrementally higher addresses. When DF is 1, the memory addresses are decremented, and the operand addresses become progressively lower. The STD instruction sets the direction flag bit, and the CLD instruction clears the bit.

**IF—Interrupt enable flag:** When this bit is set, the 80386 responds to external hardware interrupts. When the bit is reset, interrupts are disabled, and the 80386 ignores the hardware interrupt pin. Note that this bit does not affect the NMI interrupt. The processor always responds to faults (exceptions) and software interrupts regardless of the setting of the IF bit. When IF is 0, interrupts are said to be *masked*.

The STI instruction sets IF to 1, and the CLI instruction clears IF to 0. The interrupt enable flag is also modified when an IRET is executed. A POPF instruction modifies the interrupt enable flag only if the procedure executing the instruction has I/O privilege.

**TF—Trap flag:** The trap flag bit assists in debugging programs on the 80386. When the TF bit is set, an interrupt 1 occurs immediately after the next instruction executes. The trap flag is usually set by a debugger; the debug capabilities of the 80386 are covered in Chapter 5.

**SF—Sign flag:** The sign flag bit changes when arithmetic or logical instructions are executed. The sign flag bit receives the value of the high-order bit of the result and, when set to 1, indicates that the result of the instruction is negative.

```

MOV EDX, -1           ; Sign flag unchanged by MOV

ADD EDX, 3            ; EDX == 2, SF now 0

NEG EDX              ; EDX == -2, SF now 1

```

**ZF—Zero flag:** The zero flag bit is set when arithmetic instructions generate a 0 result.

```

MOV AL, 0             ; Zero flag unchanged by MOV

OR AL, AL             ; AL unchanged, ZF now 1

```

**AF—Auxiliary carry flag:** The auxiliary carry flag bit indicates that a carry out of the low-order nibble of the AL register occurred in an arithmetic instruction. This bit is used by the ASCII and BCD instructions. It allows implementation of multiple-digit precision decimal arithmetic. The following example assumes an ASCII encoding of the characters 4 and 7.

```

MOV AL, '4'           ; AL == 34H, AF unchanged by MOV

ADD AL, '7'           ; AL == 6BH, AF now 1

AAA                  ; ASCII Adjust, AL == 1, AH = AH + 1

```

**PF—Parity flag:** The parity flag bit is set to 1 when an arithmetic instruction results in a value with an even number of 1 bits. For example, if you issued the following instructions, the resulting parity flag bit would be 0.

```

MOV AH, 91H           ; AH == 10010001B, PF unchanged by MOV

ADD AH, 05H           ; AH == 10010110B, PF now 1

```

**CF—Carry flag:** The carry flag bit is set when the result of an arithmetic operation is too large or small for the destination register or memory address. It is similar in operation to the OF bit but indicates an unsigned overflow of the destination.

```

MOV AL, 127           ; AL == 7FH, CF unchanged by MOV

ADD AL, 2              ; AL == 81H, CF now 0

ADD AL, AL             ; AL == 02H, CF now 1 (result is 102H)

MOV AL, 3              ; CF unchanged by MOV

SUB AL, 4              ; AL == FFH, CF now 1 (borrow bit)

```

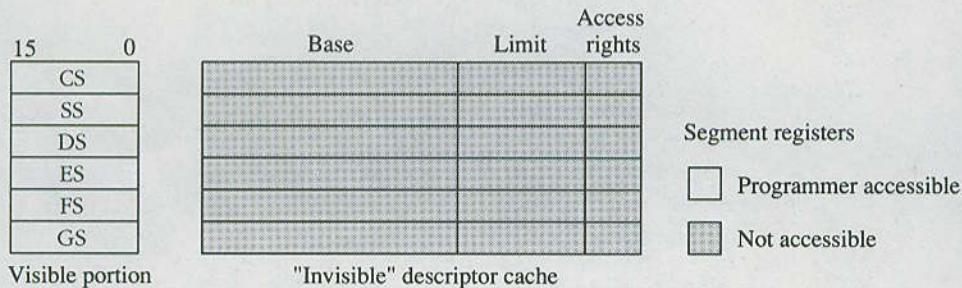

## Segment registers

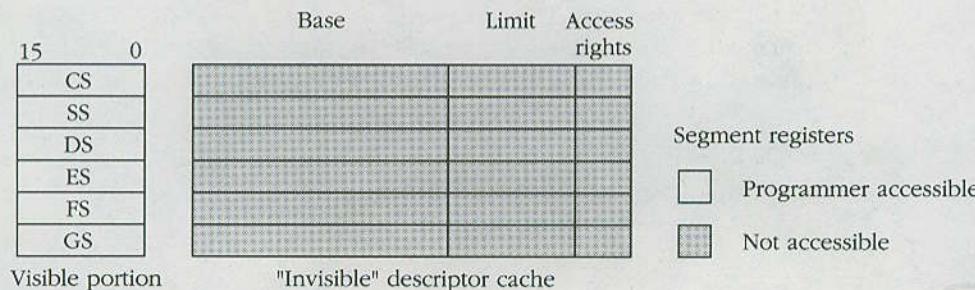

The segment registers hold the values that affect which portions of memory a program uses. Four segment registers are used under specific conditions, and two are available as pointers to frequently used areas of memory. The CS, DS, SS, and ES registers were inherited from the 80286 and perform the same functions as they did in that CPU. Two additional registers, FS and GS, are new to the 80386.

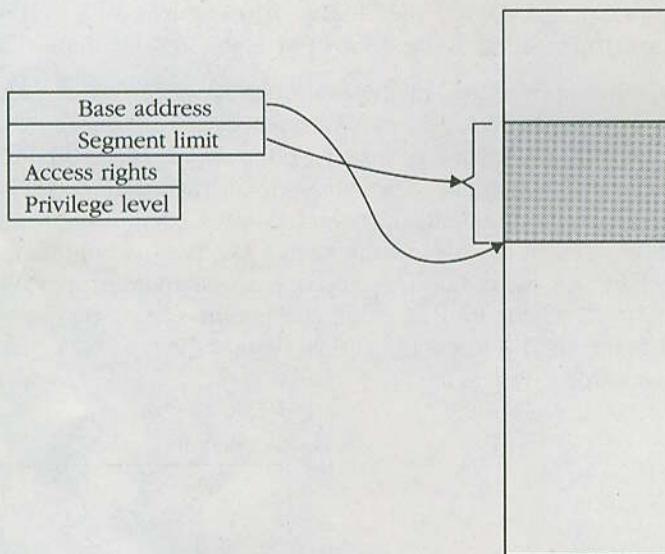

Associated with the segment registers is a descriptor cache, which holds the starting address of the memory segment and other related information. Chapter 3 details the relationship between segments and memory addresses in the 80386. The descriptor cache for the segment registers is not accessible to the programmer; only the 16-bit register portion can be accessed directly. Figure 2-13 illustrates the segment registers and the internal descriptor cache.

Figure 2-13. Segment registers.

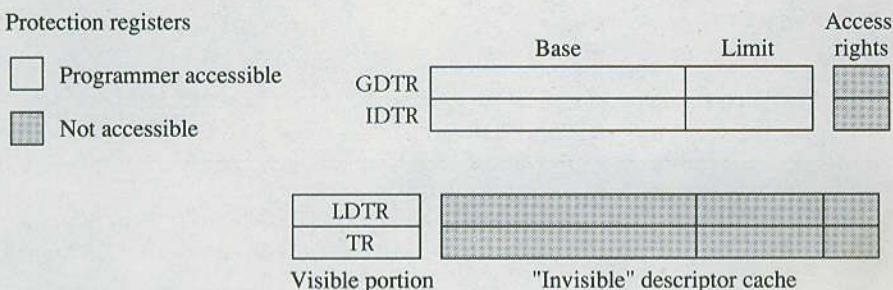

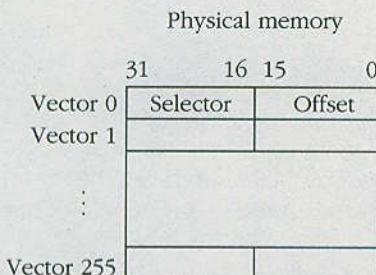

## Protection model registers

Four registers support the protection model of the 80386, as shown in Figure 2-14.

**Figure 2-14. Protection registers.**

The protection model registers are:

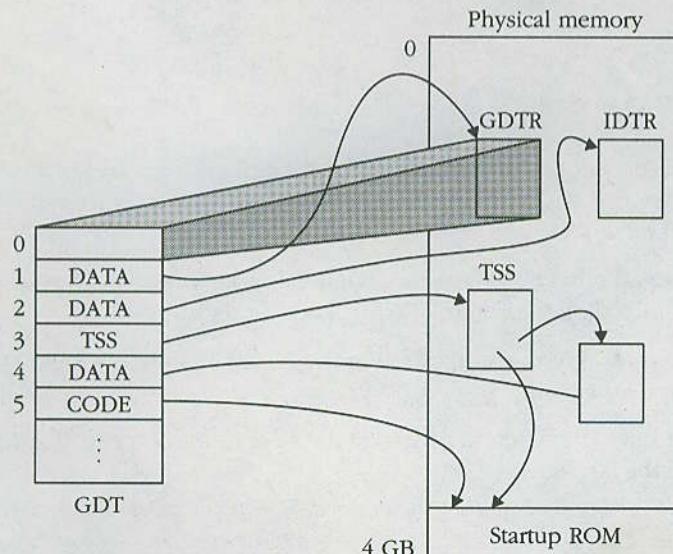

**GDTR**—Global Descriptor Table Register

**IDTR**—Interrupt Descriptor Table Register

**LDTR**—Local Descriptor Table Register

**TR**—Task Register

The GDTR and IDTR contain linear base addresses that point to the start of the GDT and the IDT descriptor tables. They also contain limit fields that describe the size of the GDT and IDT tables.

The LDTR and TR registers hold 16-bit selector values, similar to the segment registers. Like the segment registers, an inaccessible descriptor cache exists for both the LDTR and TR. The LDTR holds a selector for an LDT descriptor, and the TR holds a selector for the TSS (task state segment) of the currently executing process. Chapter 5 discusses how these registers work.

## Control registers

The control registers regulate the paging and numeric coprocessor operation of the 80386. A general description of the registers follows; refer to the specific chapters on paging and coprocessors for more detailed information. A programmer can only read or modify control registers by instructions of the form `MOV CRx, reg`, where `reg` stands for one of the general registers. A procedure must be running at the highest privilege level to execute these instructions.

**CR0—Control register 0**

The following illustration shows the contents of control register 0. The LMSW and SMSW instructions allow access to the low-order 16 bits of CR0 as the machine status word.

|        |          |     |                        |     |

|--------|----------|-----|------------------------|-----|

| 31     | 16 15    | 8 7 | 4 3 2 1 0              |     |

| P<br>G | Reserved |     | E T E M P<br>T S M P E | CR0 |

**PG—Paging:** Paging is enabled by setting the PG bit to 1. Typically, the operating system does this once, at initialization. Chapter 6 discusses the 80386 paging mechanism.

**ET—Extension type:** The 80386 sets the ET bit to 1 at boot time if the processor determines that an 80387 is present. If this bit is 0, the coprocessor is either an 80287 or is not present at all. When ET is 1, the 80386 uses a 32-bit protocol to communicate with the coprocessor; otherwise, it uses a 16-bit protocol.

**TS—Task switched:** The 80386 sets the TS bit when a task switch operation occurs. When the TS bit is on, the next coprocessor instruction causes a trap to the operating system. This feature lets the operating system implement multitasking without requiring the operating system to save the state of the math coprocessor every time a task switch occurs. The context of the 80387 is more than 100 bytes, so saving the coprocessor state at every task switch would waste valuable CPU time.

**EM—Emulate math coprocessor:** When this bit is set, floating-point instructions that would normally control coprocessor operation trap to the operating system instead. Proper use of this bit allows programmers to write applications as if a coprocessor were present. If an 80287 or 80387 is present, the operating system initializes the EM bit to 0, and the application's floating-point instructions will be executed by the coprocessor. If an 80287 or 80387 is not present, the operating system sets the EM bit to 1. Then, when an application executes a floating-point instruction, the 80386 will trap back to the operating system, which either emulates the instruction in software or passes the operands to other floating-point hardware in the system.

**MP—Math present:** The operating system sets this bit to 1 at boot time if a math coprocessor (either the 80287 or 80387) is present. The MP bit affects the operation of the WAIT instruction, as described in Chapter 8.

**PE—Protect enable:** Setting the PE bit places the processor into protected mode. Typically, this is done once, at initialization. Unlike the earlier 80286, the 80386 makes it possible to switch the CPU back into real mode after entering protected mode. Some implementations of the OS/2 operating system use this technique to allow real-mode MS-DOS programs to run concurrently with protected-mode OS/2 applications.

### CR1—Control register 1

Control register 1 is not used in the 80386 and is reserved for future Intel processors.

### CR2—Control register 2

When a page fault occurs, the CR2 register is loaded with the linear address that caused the exception. Refer to Chapter 6 for more details on paging in the 80386.

### CR3—Control register 3

The 80386 paging hardware also uses this register. It contains the linear address of the starting point of the page directory. The implementation of paging is covered fully in Chapter 6.

## Debug and test registers

The 80386 contains seven debug registers and two test registers. The test registers, TR6 and TR7, allow diagnostic software to test the translation lookaside buffer (TLB). Because the TLB is part of the paging hardware, these registers are discussed in Chapter 6.

The debug registers, labeled DR0–DR7, allow the 80386 to implement a hardware breakpoint capability that previously required an external in-circuit emulator. By setting the address register (DR0–DR3) and control bits (DR6–DR7), the programmer can halt the 80386 when a particular memory location is read from, written to, or executed. The breakpoints are noninvasive (they don't require modification of the program under debug), and they are also real-time (they don't degrade the performance of the program). Chapter 5 describes debugging techniques using the debug registers.

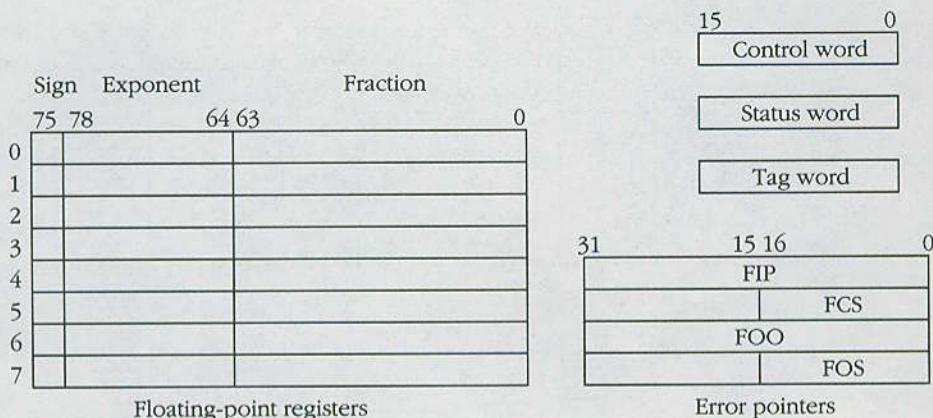

## Coprocessor Support

The 80386 can operate with either the 80287 or 80387 numeric data processor (NDP). Because these special-purpose chips operate in parallel with the 80386, they are called *coprocessors*. The 80287 is a slower chip with a 16-bit interface, originally designed for use with the 80286. Floating-point performance with the 80287 is approximately 320,000 whetstones when running at 10 MHz. The 32-bit 80387 offers higher performance. This processor is software compatible with the 80287 and can execute about 1,800,000 whetstones when running at 16 MHz. Appendix F notes the differences between the 80287 and 80387. References to the 80387 in the following text also refer to the 80287, unless otherwise noted.

In addition to the raw performance advantage of hardware support for floating-point arithmetic, the NDPs introduce another level of parallelism into the system. As soon as the 80386 passes an instruction to the 80387, it begins operating on the next instruction regardless of how long the 80387 takes to complete its operation. Of course, if the 80386 encounters another floating-point instruction, it must wait for the coprocessor to complete the current operation before the 80386 can give it another one.

To use a value computed by the 80387 and written to memory, you must ensure that the 80387 has completed the write operation. The FWAIT instruction ensures synchronization between the 80386 and 80387.

If a coprocessor is absent, the 80386 allows an operating system to emulate one and remain invisible to the application. For details on coprocessor emulation, see the discussion of the EM bit in control register 0 of the 80386 earlier in this chapter.

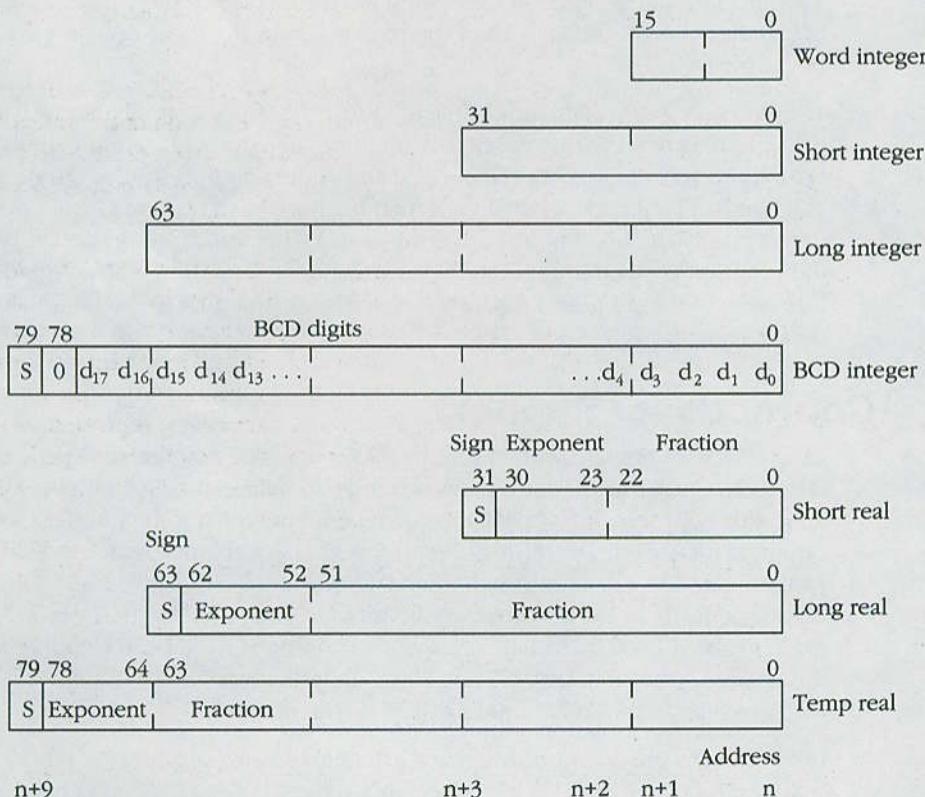

## Additional data formats

Adding either the 80287 or the 80387 coprocessor to an 80386 adds direct hardware support for three floating-point number formats and one BCD integer format. The 80287 and 80387 also support three integer formats that the 80386 recognizes. These are the 16-bit, 32-bit, and 64-bit two's complement (signed) integers, identical to their counterparts on the 80386. Figure 2-15 shows the additional numeric formats.

**Figure 2-15.** Floating-point formats.

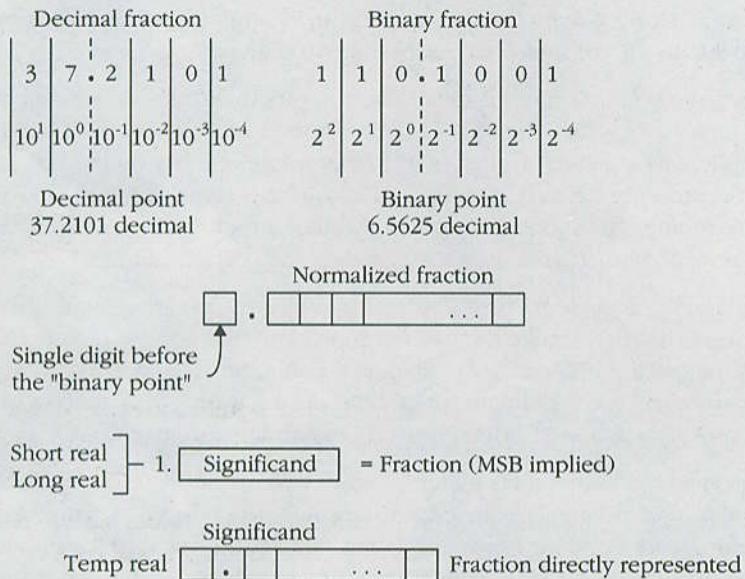

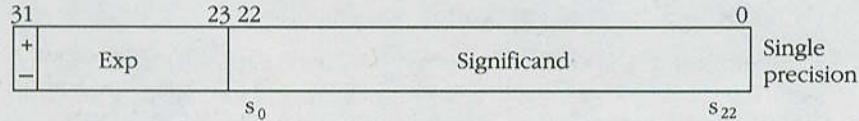

## Floating-point numbers

The 80387 supports three floating-point formats. This allows a programmer to make compromises between the amount of memory required and the precision of the results. The *short real* format lets programmers specify numbers of about six decimal digits of accuracy. This format is also known as *single-precision* because a short real number fits into a single 32-bit machine word. *Long reals*, also known as *double-precision*, represent floating-point numbers of up to 15 decimal digits of accuracy. Holding a long real number requires a double machine word (64 bits). The third format is called *temp (temporary) real* or *extended-precision*. Temp real numbers are 80 bits and represent about 19 decimal digits of precision.

Just as scientific notation represents floating-point quantities in decimal notation (for example,  $4.74 \times 10^3$ ), the 80387 floating-point format is a type of binary scientific notation. The general format of a floating-point number on the 80387 is  $\pm f \times 2^e$ , where  $f$  represents a binary fraction and  $e$  is an exponential power of 2. Three fields are required to make up a floating-point number: the sign, the exponent, and the fraction, or *significand*.

The sign field is a single bit that is set to 1 to indicate a negative number and reset to 0 for a positive value. Unlike the two's complement notation of the integers, no value manipulation is necessary to change the number from positive to negative (or vice versa) other than toggling the sign bit. This notational format allows the representation of +0.0 and -0.0, which is useful in certain circumstances.

The exponent field represents a multiplier of  $2^e$ . This field ranges from 8 bits in the short real format to 11 bits in the long real format to 15 bits in the temp real format. To accommodate negative exponents (such as  $2^{-6}$ ), the value in the exponent field is *biased*; that is, the actual exponent is determined by subtracting the appropriate bias value from the value in the exponent field. For example, the bias for short reals is 127. If the value in the exponent field is 130, the exponent represents a value of  $2^{130-127}$ , or  $2^3$ . The bias for long reals is 1023, and the bias for temp reals is 16383. The values 0 and all 1s (binary) are reserved for representing special values and cannot be used to represent floating-point numbers.

The significand field contains the fractional part of the floating-point number. The significand occupies 23 bits in short reals, 52 bits in long reals, and 64 bits in temp reals. Figure 2-16 shows how to interpret floating-point fractions. The significand is encoded in two different ways on the 80387. In temp real format, the significand field holds the binary fraction in the form  $s_0.s_1s_2\dots s_{63}$ , where  $s_n$  is bit  $n$  of the significand.

In short format and in long real format, the authors of the IEEE-754 format took advantage of a representational trick to squeeze out an extra bit of precision. A review of scientific notation shows that the values  $40.103 \times 10^7$ ,  $4.0103 \times 10^8$ , and  $0.0040103 \times 10^{10}$  all represent the same number. A binary notation has the same property.

Shifting the fraction by one position can be compensated for by incrementing or decrementing the value of the exponent. Because a binary number consists of only 0s and 1s, the designers of the floating-point format decided that the fractional portion of the short and long reals would be shifted left until the most significant bit was 1. Since this bit was now *defined* as 1, there was no point in storing it, and it was assumed to exist. The fraction for a short or long real, therefore, has the value  $1.s_0s_1s_2\dots s_n$ , where  $n$  is 22 for short reals and 51 for long reals.

Figure 2-16. Floating-point fractions.

**Short real:**

$$\text{Absolute value} = 1.s_0s_1\dots s_{22} \times 2^{(\text{exp} - 127)}$$

The bias for the short real exponent is 127. The significand includes the "implied 1" bit and allows a precision of about six decimal digits. Representative values range from  $\pm 1.18 \times 10^{-38}$  to  $\pm 3.40 \times 10^{38}$ .

**Long real:**

|       |       |                    |                  |

|-------|-------|--------------------|------------------|

| 63 62 | 52 51 | 0                  |                  |

| +/-   | Exp   | Significand        | Double precision |

|       |       | $s_0 \dots s_{51}$ |                  |

$$\text{Absolute value} = 1.s_0s_1\dots s_{51} \times 2^{(\text{exp} - 1023)}$$

The bias for the long real exponent is 1023. The significand includes the “implied 1” bit and allows a precision of about 15 decimal digits. Representative values range from  $\pm 2.23 \times 10^{-308}$  to  $\pm 1.80 \times 10^{308}$ .

**Temp real:**

|       |       |                    |                    |

|-------|-------|--------------------|--------------------|

| 79 78 | 64 63 | 0                  |                    |

| +/-   | Exp   | Significand        | Extended precision |

|       |       | $s_0 \dots s_{63}$ |                    |

$$\text{Absolute value} = s_0.s_1\dots s_{63} \times 2^{(\text{exp} - 16383)}$$

The bias for the temp real exponent is 16383. The significand represents the fractional portion of the value (with no implied bits) and allows a precision of about 19 decimal digits. Representative values range from  $\pm 3.30 \times 10^{-4932}$  to  $\pm 1.2 \times 10^{4932}$ .

**Special floating-point values:** In addition to intuitive values such as 3.14159 and  $6.03 \times 10^{23}$ , the 80387 represents values that arise under unusual conditions. These values are called *infinities*, *denormals*, and *NaNs*. (NaN stands for “not a number.”)

Infinity, positive or negative, is represented by a value whose exponent field is all 1s and whose fraction is 1.0B. Note that in short and long real numbers, 1.0B is represented by a significand of all 0s, whereas in temp real numbers, the significand is a binary 10000000...0B.

Denormals are values that are too small to represent in the standard (or normalized) fashion. Denormals are represented by a value with an exponent field of 0 and any nonzero value in the significand. A floating-point number with both an exponent of 0 and a significand of 0 represents 0.0.

NaNs are invalid representations of floating-point numbers. They are identified by an exponent field of all 1s and a significand other than the one representing infinity. The two kinds of NaNs are the signaling NaN and the quiet NaN. A signaling NaN has a fraction of the form 1.0xxx...xB, where x represents any bit value. The 80387 generates an exception whenever a signaling NaN is used. The 80387 never creates

a signaling NaN, but a programmer can use one to indicate some error condition such as an uninitialized floating-point variable. The quiet NaN has a fractional format of 1.1xxxxxB. Recall that the leading 1 is not implied in the significand of short and long reals but must be present in temp reals. The 80387 generates a quiet NaN instead of a numeric result whenever a floating-point instruction causes an invalid operation. Any instruction that receives either type of NaN as an operand generates a NaN as a result. The following table lists special values used by the 80387.

| <i>Sign</i> | <i>Exponent</i> | <i>Fraction</i> | <i>Value</i>  |

|-------------|-----------------|-----------------|---------------|

| x           | 11...11B        | 1.1xx...xxB     | Quiet NaN     |

| x           | 11...11B        | 1.0xx...xxB     | Signaling NaN |

| x           | 11...11B        | 1.00...0B       | Infinity      |

| x           | 00...00B        | 0.xxxxxxB       | Denormals     |

| x           | 00...00B        | 0.00...0B       | Zero          |

The "x" indicates that it makes no difference whether the bit is 0 or 1. The "1" before the decimal in the fraction is physically present only in temporary real format. It is implied in the short and the long real formats. Denormals are recognized in the short and the long format by the 0 exponent value.

### **BCD integer**

The other new data type that the 80387 supports is a packed decimal integer of 18 digits stored in 10 consecutive bytes of memory. The high-order bit of the high-order byte is interpreted as a sign bit in the same way as floating-point numbers. The rest of the high-order byte is unused. The remaining bytes each contain two BCD digits.

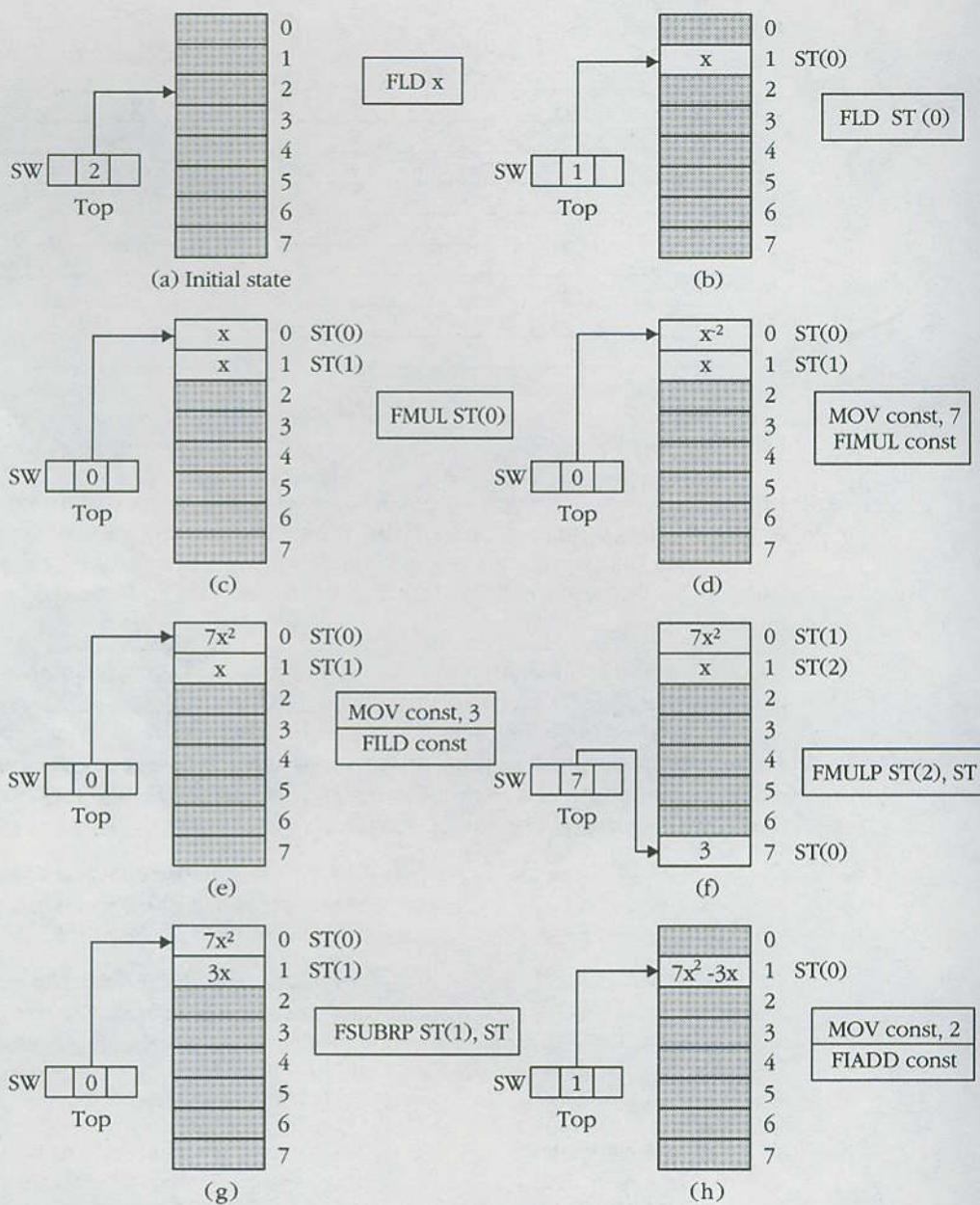

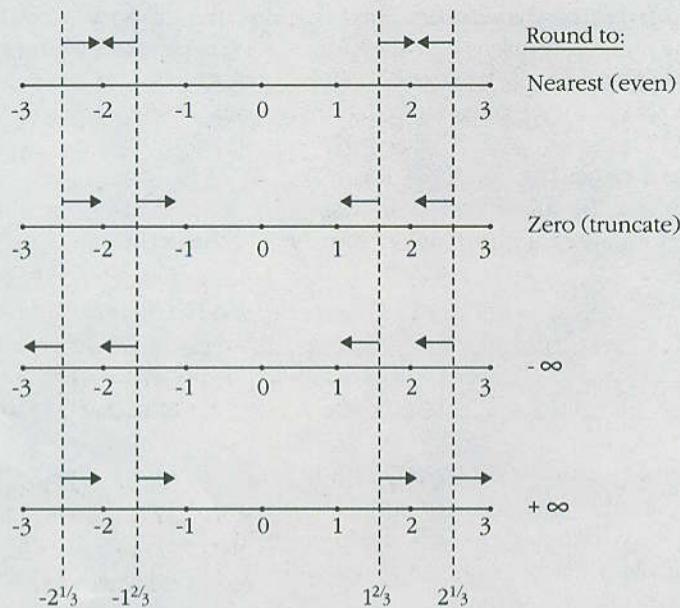

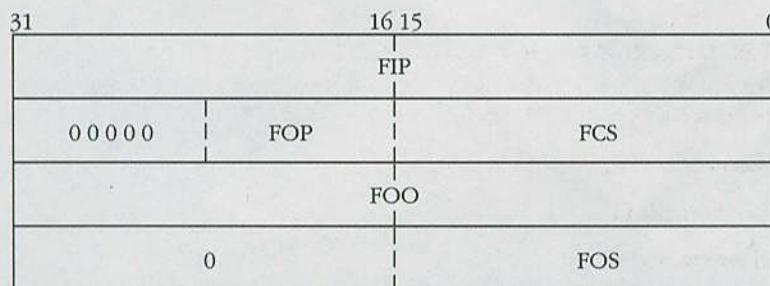

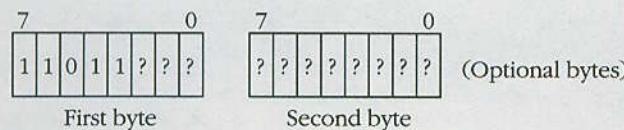

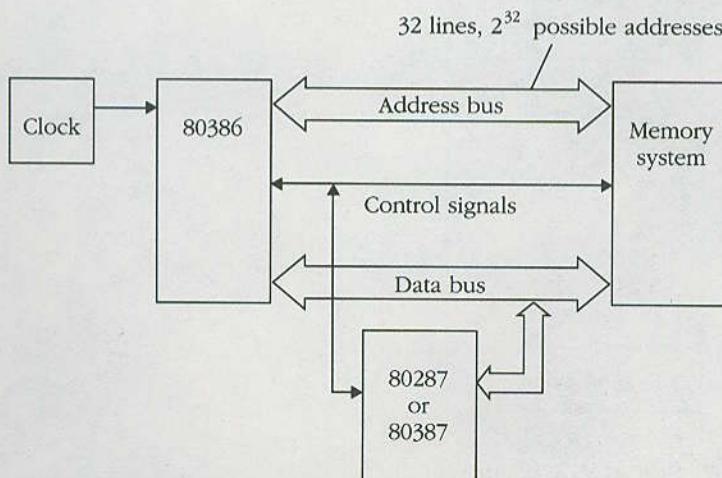

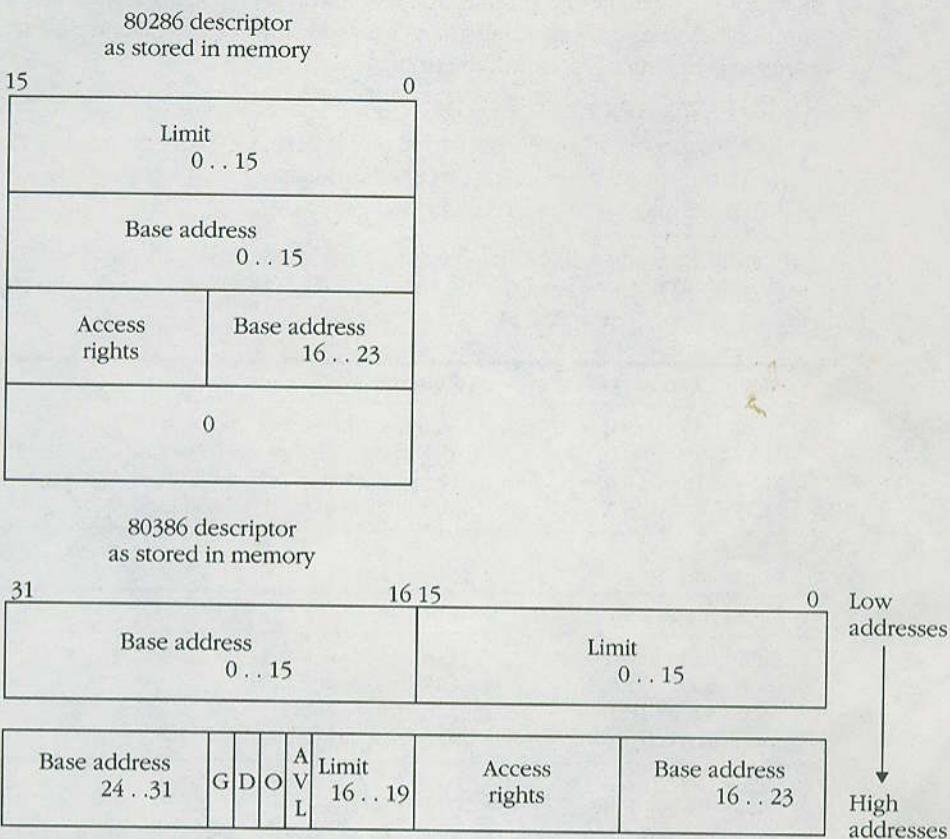

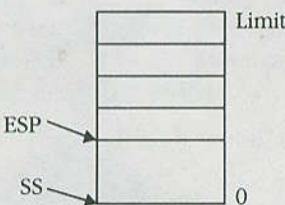

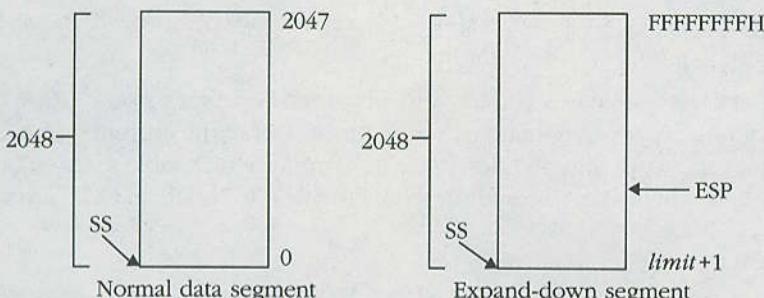

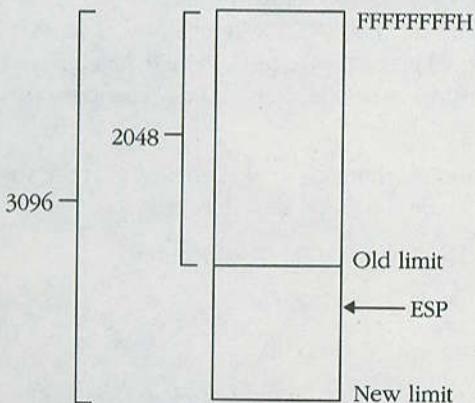

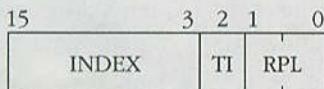

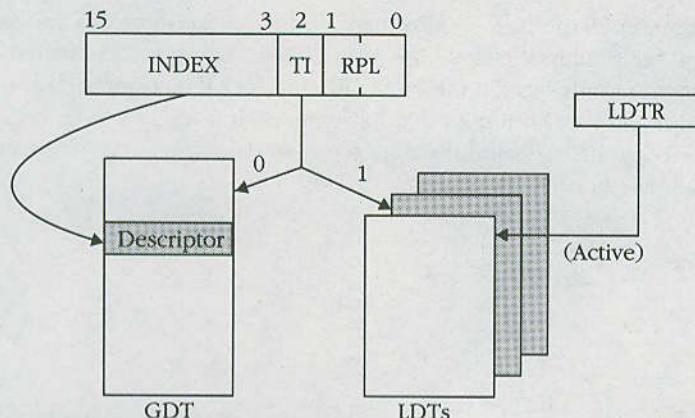

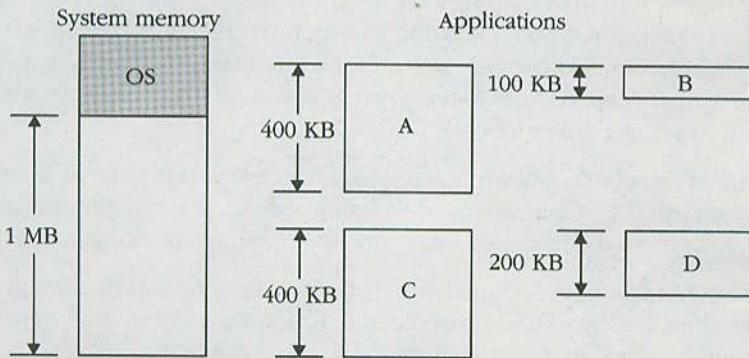

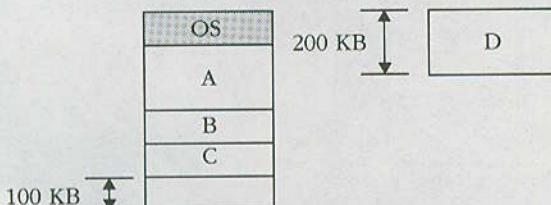

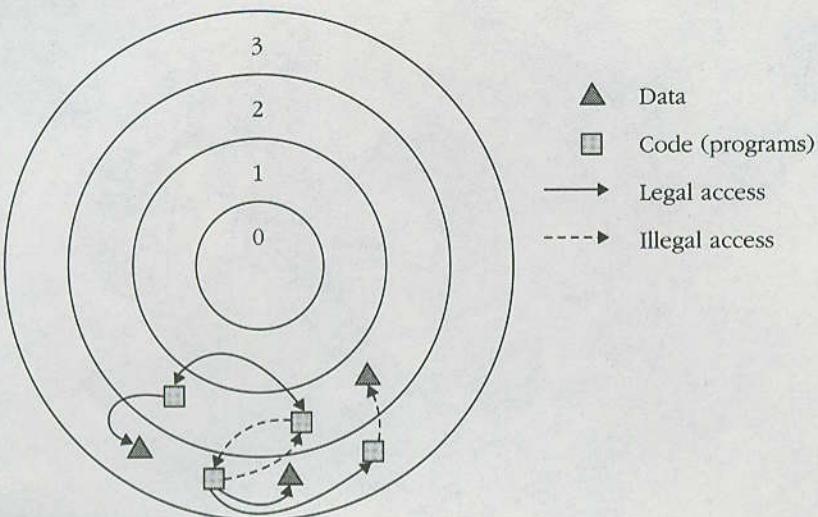

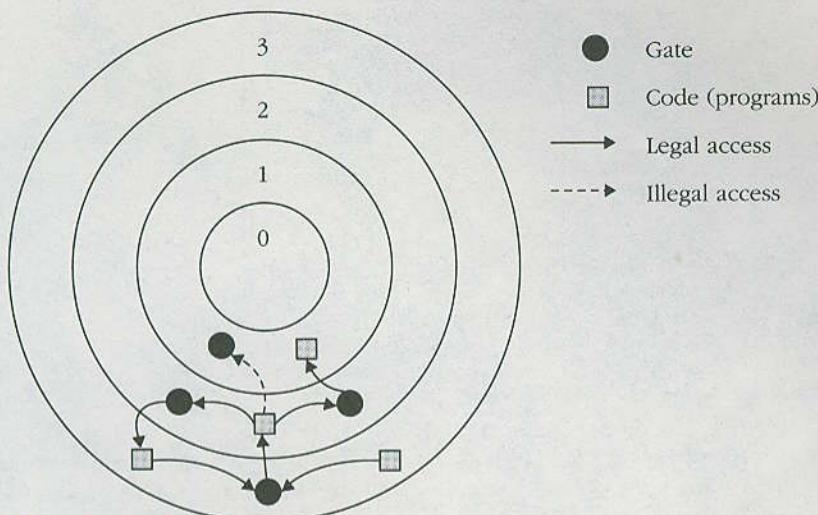

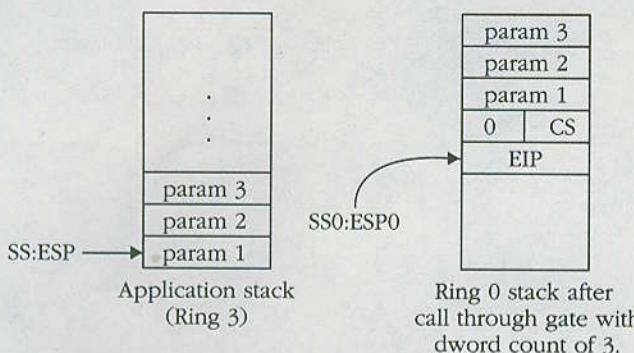

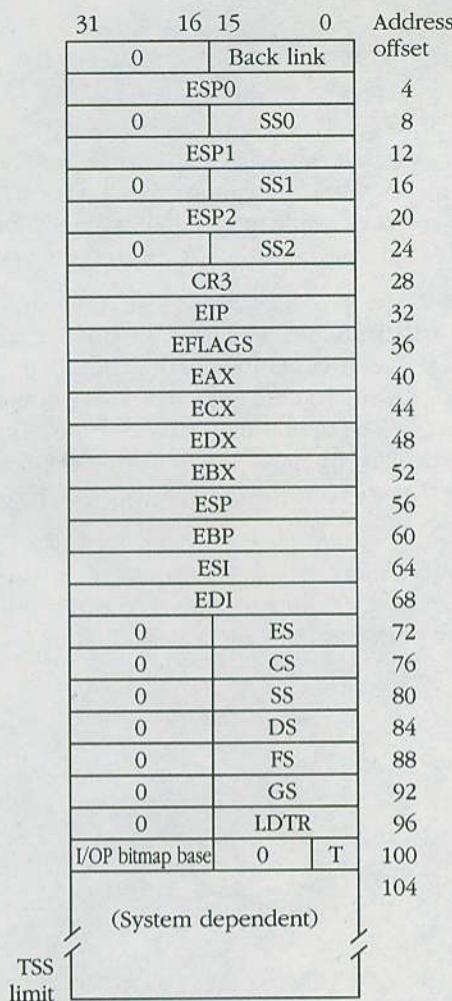

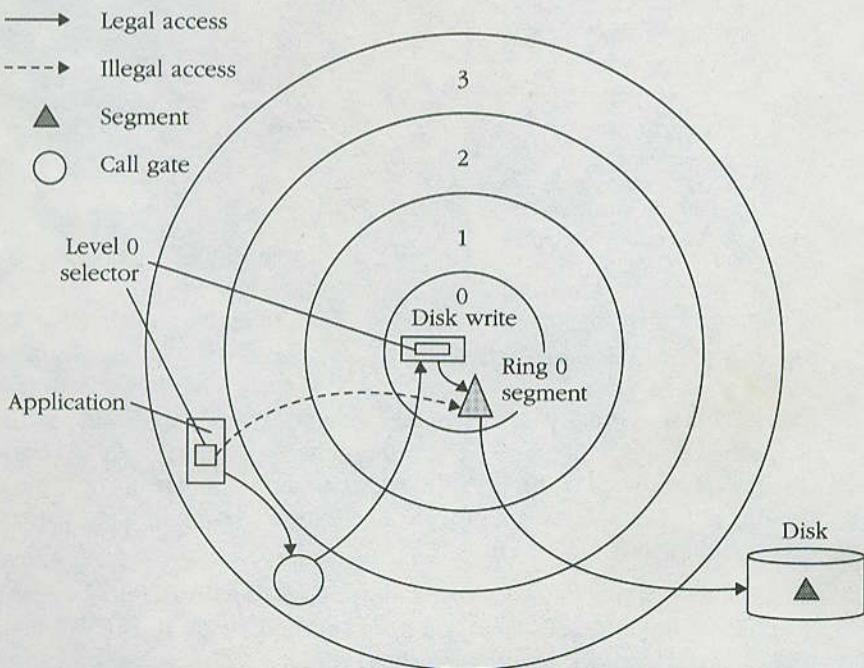

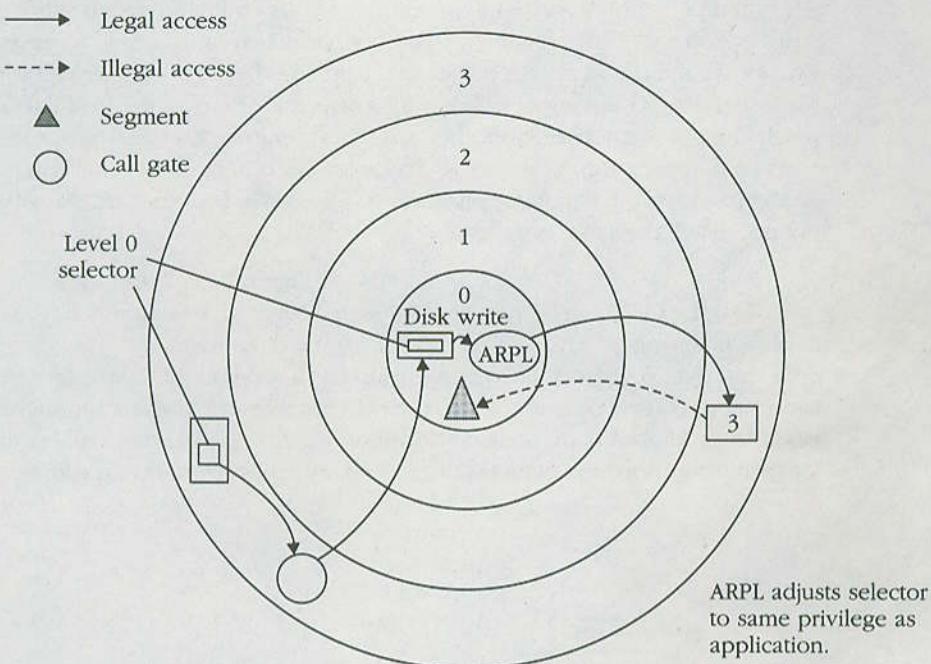

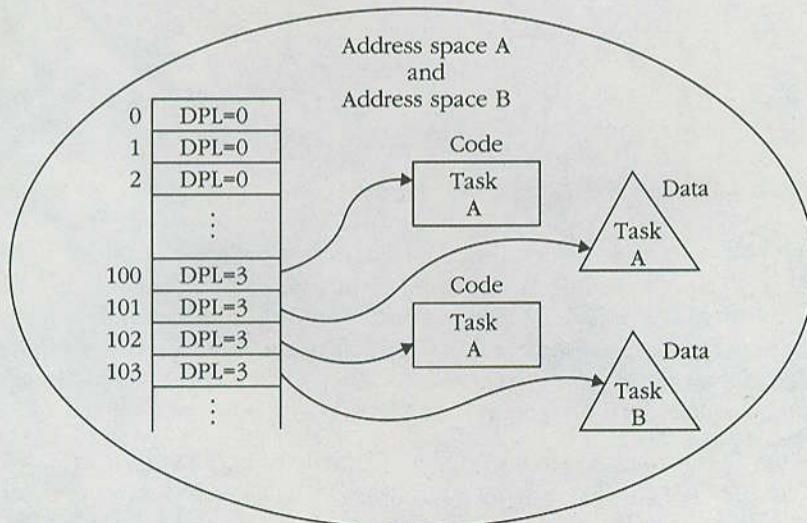

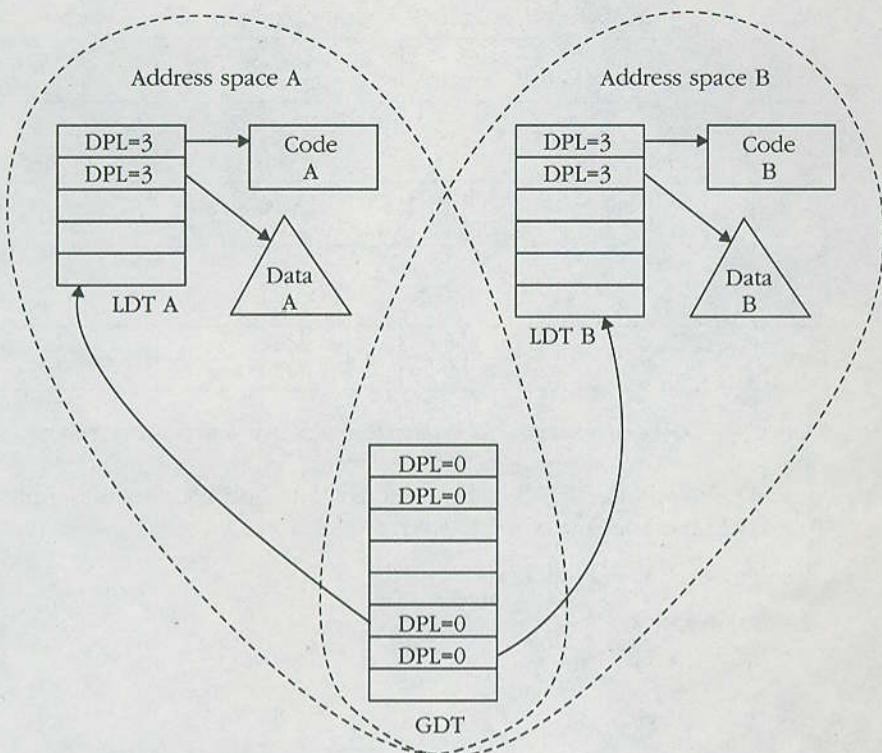

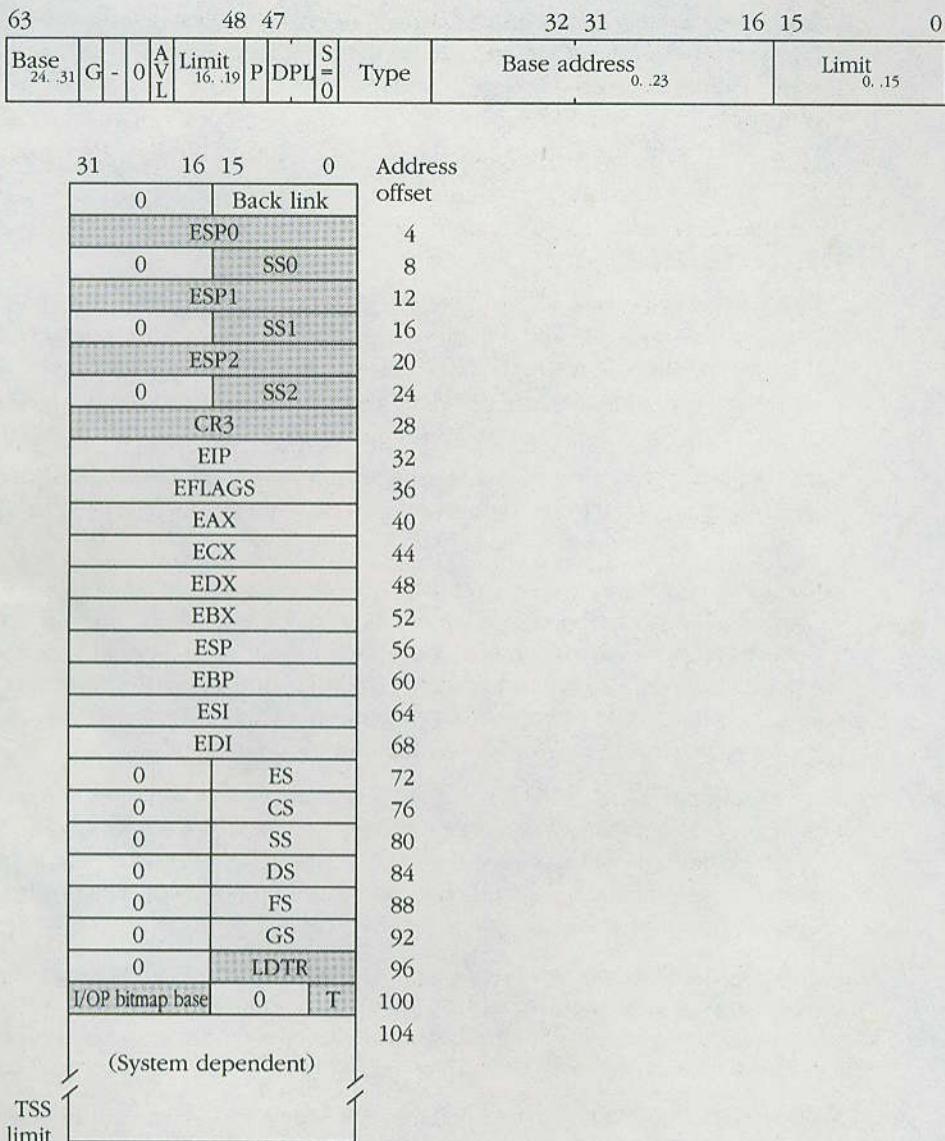

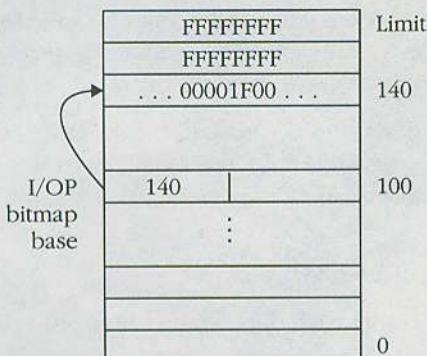

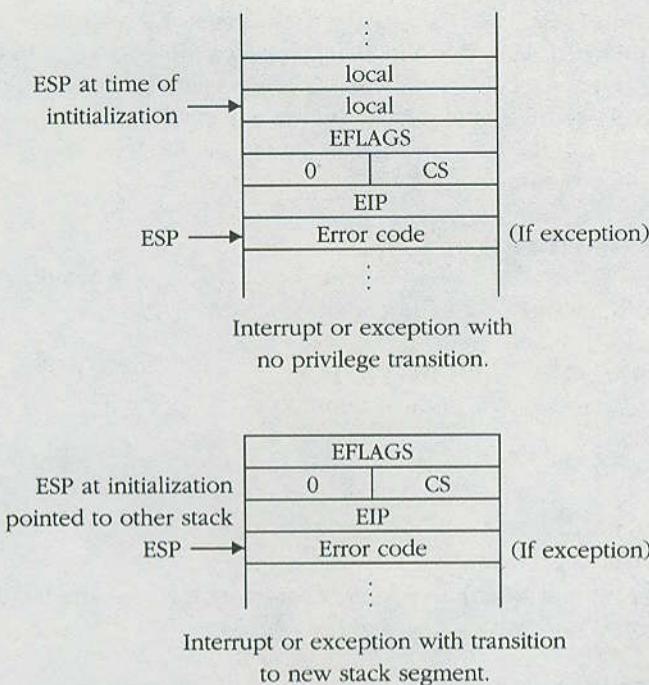

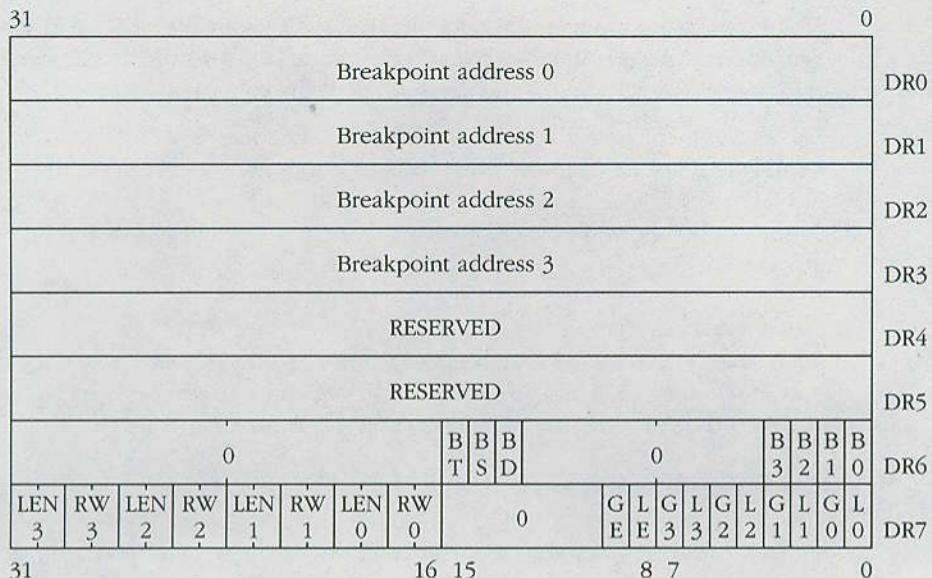

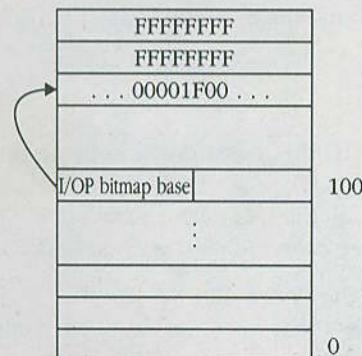

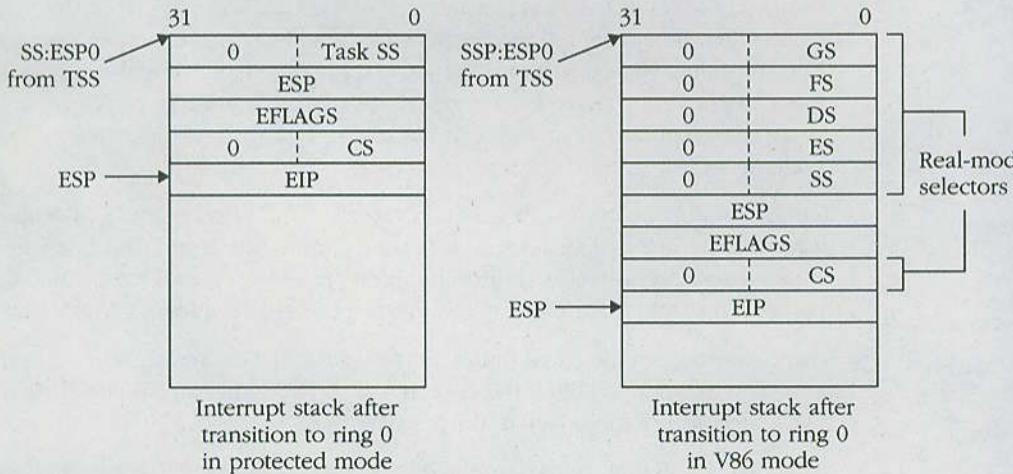

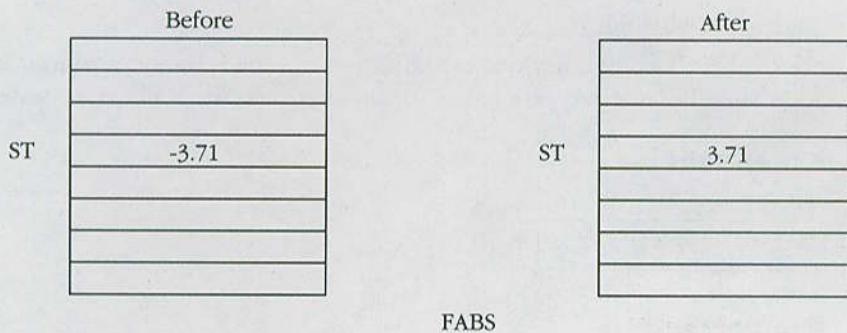

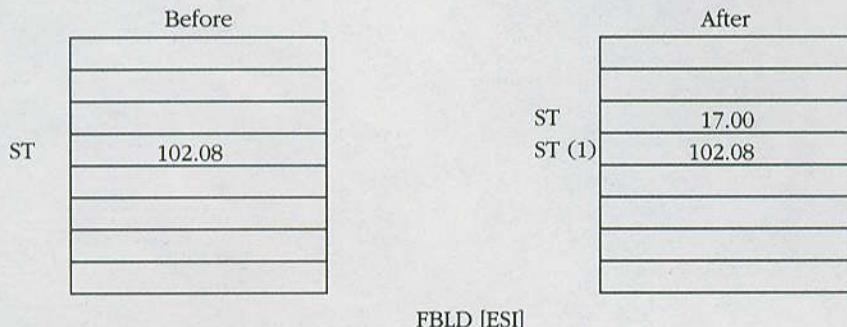

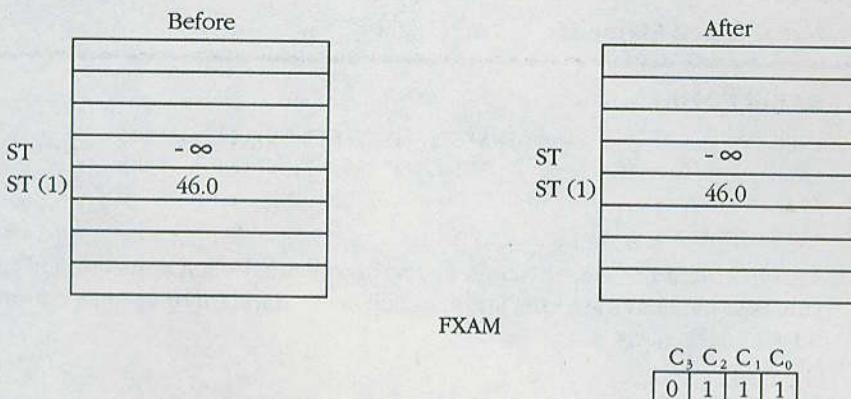

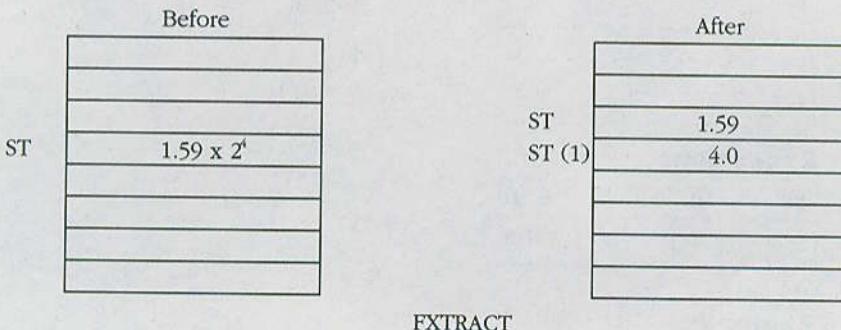

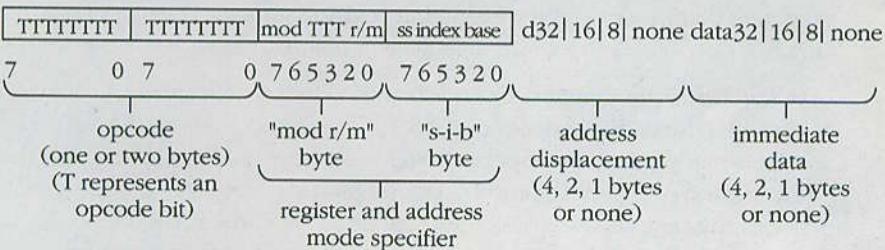

| 79 | 72 | 71  | 64  | 63  | 56  | 55  | 48  | 47  | 40  | 39  | 32  | 31  | 24  | 23  | 16  | 15  | 8   | 7   | 0 |