PRINCIPLES OF

Computer

Organization

and Assembly

Language

Using the Java® Virtual Machine

PATRICK JUOLA

# **Principles of Computer Organization and Assembly Language**

**Using the Java™ Virtual Machine**

**PATRICK JUOLA**

**Duquesne University**

Upper Saddle River, New Jersey 07458

**Library of Congress Cataloging-in-Publication Data**

Juola, Patrick

Principles of computer organization and Assembly language : using the Java virtual machine / Patrick Juola.

p. cm.

Includes bibliographical references and index.

ISBN 0-13-148683-7

1. Computer organization. 2. Assembler language (Computer program language) 3. Java virtual machine. I. Title.

QA76.9.C643J96 2006

004.2'2--dc22

2006034154

Vice President and Editorial Director, ECS: *Marcia J. Horton*

Executive Editor: *Tracy Dunkelberger*

Associate Editor: *Carole Snyder*

Editorial Assistant: *Christianne Lee*

Executive Managing Editor: *Vince O'Brien*

Managing Editor: *Camille Trentacoste*

Production Editor: *Karen Ettinger*

Director of Creative Services: *Paul Belfanti*

Creative Director: *Juan Lopez*

Cover Art Director: *Jayne Conte*

Cover Designer: *Kiwi Design*

Cover Photo: *Getty Images, Inc.*

Managing Editor, AV Management and Production: *Patricia Burns*

Art Editor: *Gregory Dulles*

Manufacturing Manager, ESM: *Alexis Heydt-Long*

Manufacturing Buyer: *Lisa McDowell*

Executive Marketing Manager: *Robin O'Brien*

Marketing Assistant: *Mack Patterson*

© 2007 Pearson Education, Inc.

Pearson Prentice Hall

Pearson Education, Inc.

Upper Saddle River, New Jersey 07458

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Pearson Prentice Hall® is a trademark of Pearson Education, Inc.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of these programs.

Printed in the United States of America

All other trademarks or product names are the property of their respective owners.

**TRADEMARK INFORMATION**

Java is a registered trademark of Sun Microsystems, Inc.

Pentium is a trademark of Intel Corporation.

Visual C++ is a registered trademark of Microsoft Corporation.

PowerPC is a registered trademark of IBM Corporation.

10 9 8 7 6 5 4 3 2 1

ISBN 0-13-148683-7

Pearson Education Ltd., *London*

Pearson Education Australia Pty. Ltd., *Sydney*

Pearson Education Singapore, Pte. Ltd.

Pearson Education North Asia Ltd., *Hong Kong*

Pearson Education Canada, Inc., *Toronto*

Pearson Educación de Mexico, S.A. de C.V.

Pearson Education—Japan, *Tokyo*

Pearson Education Malaysia, Pte. Ltd.

Pearson Education, Inc., *Upper Saddle River, New Jersey*

*To My Nieces*

*Lyric Elizabeth, Jayce Rebekah, and Trinity Elizabeth*

*This page intentionally left blank*

# Contents

---

## Preface xiii

### Statement of Aims xiii

- What xiii

- How xiv

- For Whom xiv

## Acknowledgments xv

## I Part the First: Imaginary Computers 1

### 1 Computation and Representation 3

#### 1.1 Computation 3

- 1.1.1 Electronic Devices 3

- 1.1.2 Algorithmic Machines 4

- 1.1.3 Functional Components 4

#### 1.2 Digital and Numeric Representations 9

- 1.2.1 Digital Representations and Bits 9

- 1.2.2 Boolean Logic 12

- 1.2.3 Bytes and Words 13

- 1.2.4 Representations 14

#### 1.3 Virtual Machines 27

- 1.3.1 What is a “Virtual Machine”? 27

- 1.3.2 Portability Concerns 29

- 1.3.3 Transcending Limitations 30

- 1.3.4 Ease of Updates 30

- 1.3.5 Security Concerns 31

- 1.3.6 Disadvantages 31

#### 1.4 Programming the JVM 32

- 1.4.1 Java: What the JVM Isn’t 32

- 1.4.2 Translations of the Sample Program 34

- 1.4.3 High- and Low-Level Languages 35

- 1.4.4 The Sample Program as the JVM Sees It 37

#### 1.5 Chapter Review 38

**1.6 Exercises 39****1.7 Programming Exercises 41****2 Arithmetic Expressions 42****2.1 Notations 42**

- 2.1.1 Instruction Sets 42

- 2.1.2 Operations, Operands, and Ordering 43

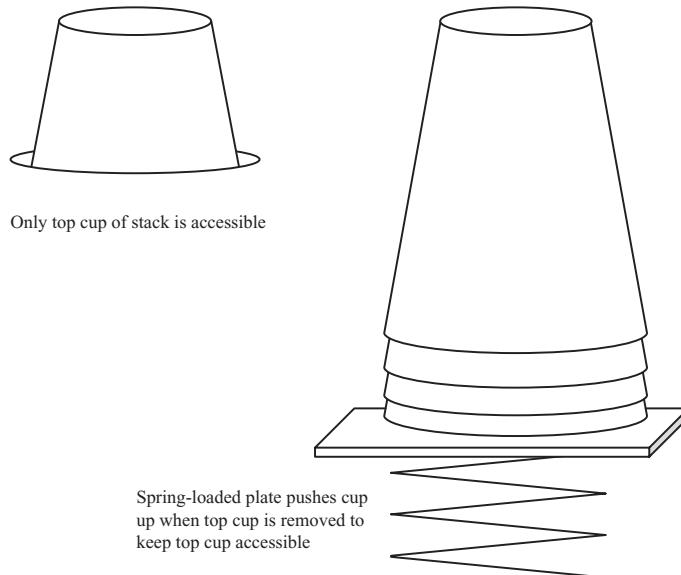

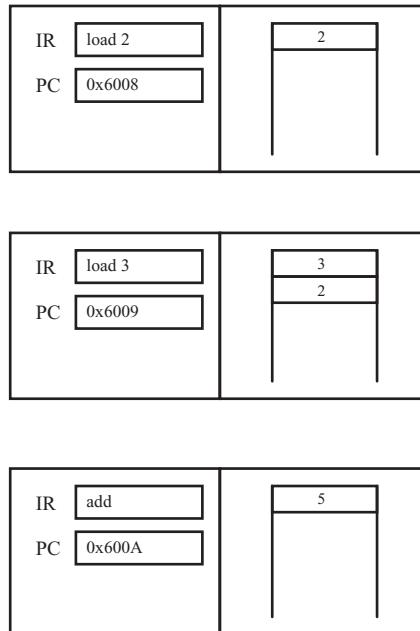

- 2.1.3 Stack-Based Calculators 43

**2.2 Stored-Program Computers 45**

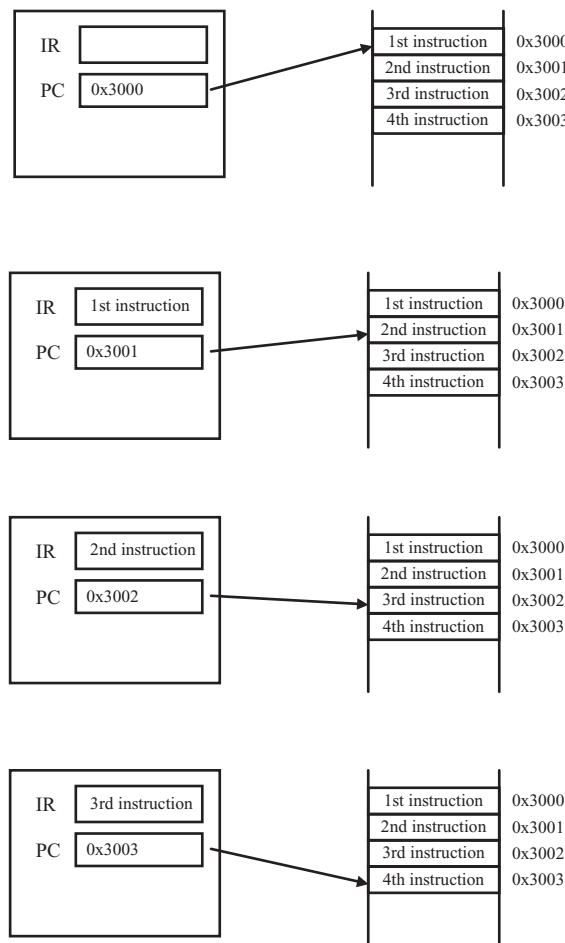

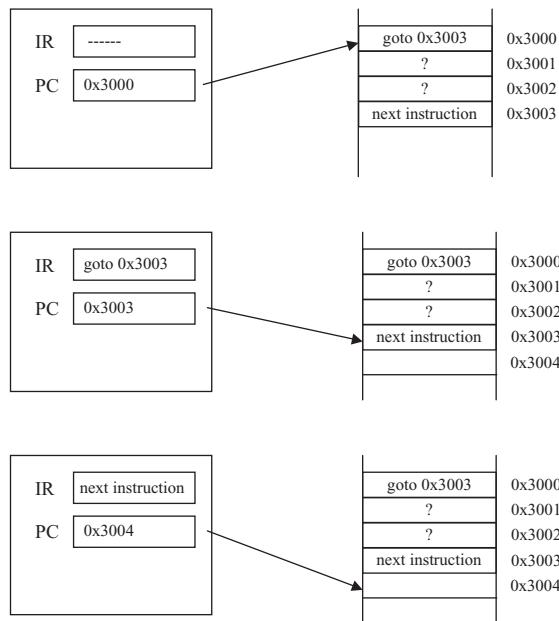

- 2.2.1 The fetch-execute Cycle 45

- 2.2.2 CISC vs. RISC Computers 48

**2.3 Arithmetic Calculations on the JVM 49**

- 2.3.1 General Comments 49

- 2.3.2 A Sample Arithmetic Instruction Set 50

- 2.3.3 Stack Manipulation Operations 53

- 2.3.4 Assembly Language and Machine Code 55

- 2.3.5 Illegal Operations 56

**2.4 An Example Program 57**

- 2.4.1 An Annotated Example 57

- 2.4.2 The Final JVM Code 60

**2.5 JVM Calculation Instructions Summarized 60****2.6 Chapter Review 61****2.7 Exercises 62****2.8 Programming Exercises 63****3 Assembly Language Programming in jasmin 64****3.1 Java, the Programming System 64****3.2 Using the Assembler 66**

- 3.2.1 The Assembler 66

- 3.2.2 Running a Program 66

- 3.2.3 Display to the Console vs. a Window 67

- 3.2.4 Using System.out and System.in 68

**3.3 Assembly Language Statement Types 71**

- 3.3.1 Instructions and Comments 71

- 3.3.2 Assembler Directives 72

- 3.3.3 Resource Directives 73

**3.4 Example: Random Number Generation 73**

- 3.4.1 Generating Pseudorandom Numbers 73

- 3.4.2 Implementation on the JVM 74

- 3.4.3 Another Implementation 76

- 3.4.4 Interfacing with Java Classes 77

**3.5 Chapter Review 79****3.6 Exercises 79****3.7 Programming Exercises 80****4 Control Structures 82****4.1 “Everything They’ve Taught You Is Wrong” 82**

- 4.1.1 Fetch-Execute Revisited 82

- 4.1.2 Branch Instructions and Labels 83

- 4.1.3 “Structured Programming” a Red Herring 83

- 4.1.4 High-Level Control Structures and Their Equivalents 85

**4.2 Types of Gotos 86**

- 4.2.1 Unconditional Branches 86

- 4.2.2 Conditional Branches 86

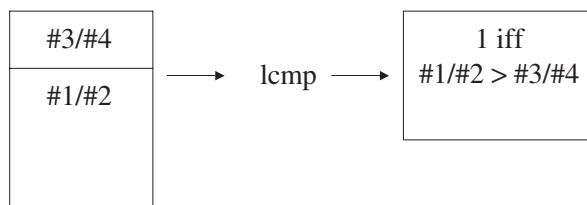

- 4.2.3 Comparison Operations 87

- 4.2.4 Combination Operations 88

**4.3 Building Control Structures 89**

- 4.3.1 If Statements 89

- 4.3.2 Loops 90

- 4.3.3 Details of Branch Instructions 92

**4.4 Example: Syracuse Numbers 94**

- 4.4.1 Problem Definition 94

- 4.4.2 Design 94

- 4.4.3 Solution and Implementation 96

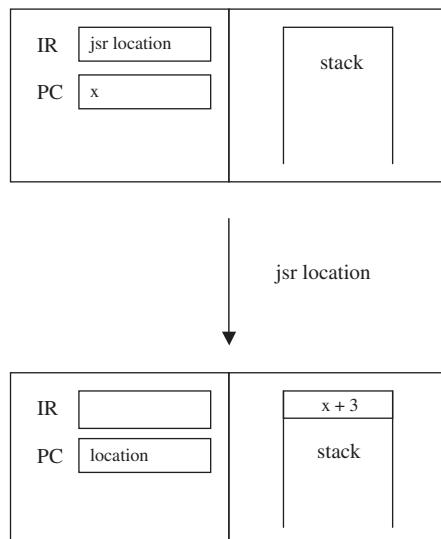

**4.5 Table Jumps 97****4.6 Subroutines 101**

- 4.6.1 Basic Instructions 101

- 4.6.2 Examples of Subroutines 102

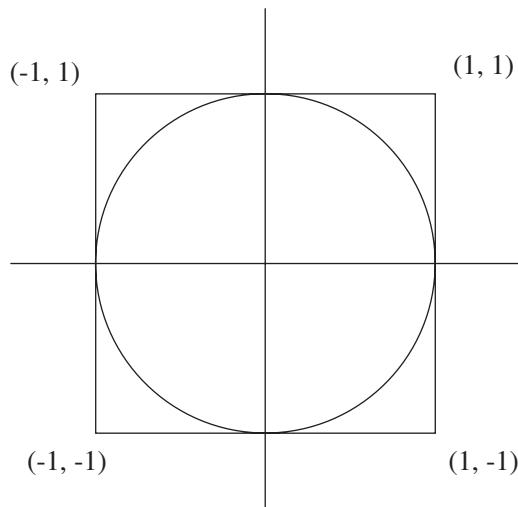

**4.7 Example: Monte Carlo Estimation of  $\pi$  105**

- 4.7.1 Problem Definition 105

- 4.7.2 Design 106

- 4.7.3 Solution and Implementation 109

**4.8 Chapter Review 111**

- 4.9 Exercises 112

- 4.10 Programming Exercises 112

## II Part the Second: Real Computers 113

### 5 General Architecture Issues: Real Computers 115

#### 5.1 The Limitations of a Virtual Machine 115

#### 5.2 Optimizing the CPU 116

- 5.2.1 Building a Better Mousetrap 116

- 5.2.2 Multiprocessing 116

- 5.2.3 Instruction Set Optimization 117

- 5.2.4 Pipelining 117

- 5.2.5 Superscalar Architecture 120

#### 5.3 Optimizing Memory 121

- 5.3.1 Cache Memory 121

- 5.3.2 Memory Management 122

- 5.3.3 Direct Address Translation 122

- 5.3.4 Page Address Translation 122

#### 5.4 Optimizing Peripherals 124

- 5.4.1 The Problem with Busy-Waiting 124

- 5.4.2 Interrupt Handling 125

- 5.4.3 Communicating with the Peripherals: Using the Bus 126

#### 5.5 Chapter Review 126

#### 5.6 Exercises 127

### 6 The Intel 8088 128

#### 6.1 Background 128

#### 6.2 Organization and Architecture 129

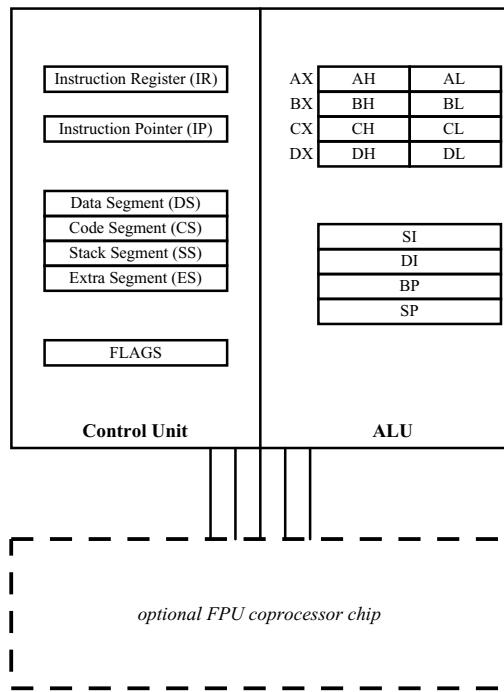

- 6.2.1 The Central Processing Unit 129

- 6.2.2 The Fetch-Execute Cycle 131

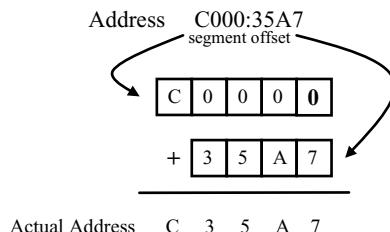

- 6.2.3 Memory 131

- 6.2.4 Devices and Peripherals 133

#### 6.3 Assembly Language 133

- 6.3.1 Operations and Addressing 133

- 6.3.2 Arithmetic Instruction Set 136

- 6.3.3 Floating Point Operations 137

- 6.3.4 Decisions and Control Structures 139

- 6.3.5 Advanced Operations 142

## **6.4 Memory Organization and Use 143**

- 6.4.1 Addresses and Variables 143

- 6.4.2 Byte Swapping 144

- 6.4.3 Arrays and Strings 145

- 6.4.4 String Primitives 147

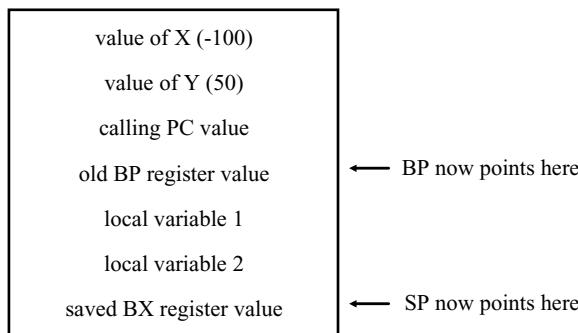

- 6.4.5 Local Variables and Information Hiding 150

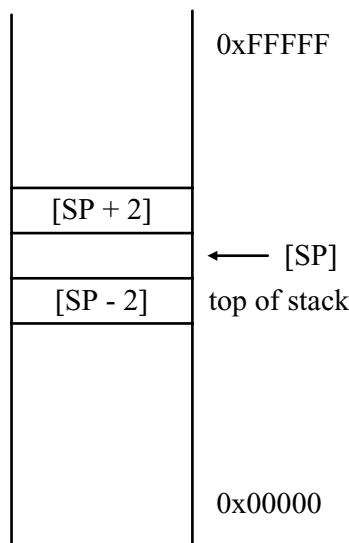

- 6.4.6 System Stack 151

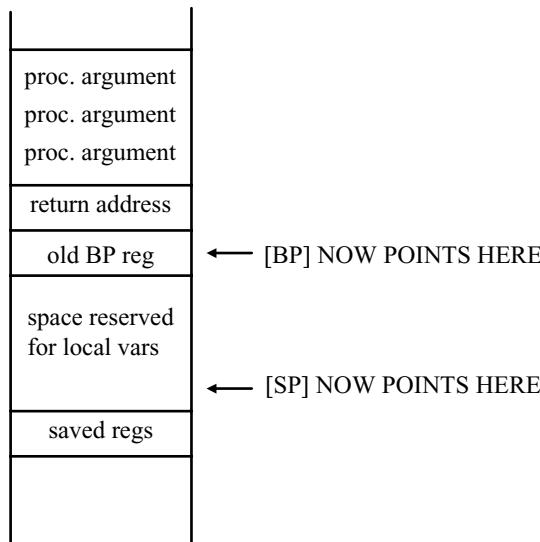

- 6.4.7 Stack Frames 152

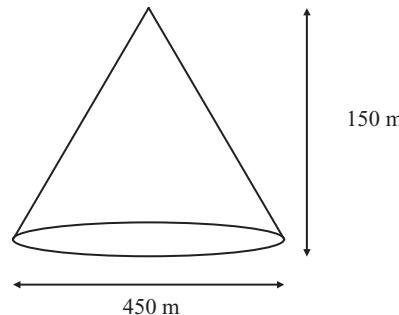

## **6.5 Conical Mountains Revisited 156**

## **6.6 Interfacing Issues 157**

## **6.7 Chapter Review 158**

## **6.8 Exercises 159**

# **7 The Power Architecture 160**

## **7.1 Background 160**

## **7.2 Organization and Architecture 161**

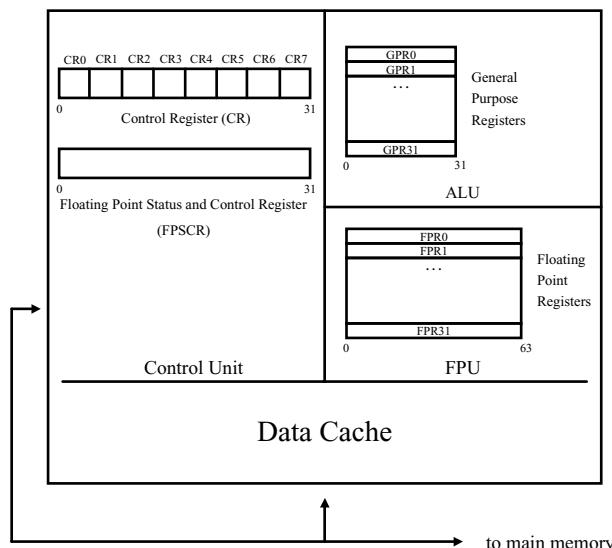

- 7.2.1 Central Processing Unit 162

- 7.2.2 Memory 163

- 7.2.3 Devices and Peripherals 163

## **7.3 Assembly Language 164**

- 7.3.1 Arithmetic 164

- 7.3.2 Floating Point Operations 166

- 7.3.3 Comparisons and Condition Flags 166

- 7.3.4 Data Movement 167

- 7.3.5 Branches 168

## **7.4 Conical Mountains Revisited 169**

## **7.5 Memory Organization and Use 170**

## **7.6 Performance Issues 171**

- 7.6.1 Pipelining 171

## **7.7 Chapter Review 174**

## **7.8 Exercises 174**

## **8 The Intel Pentium 175**

### **8.1 Background 175**

### **8.2 Organization and Architecture 176**

8.2.1 The Central Processing Unit 176

8.2.2 Memory 177

8.2.3 Devices and Peripherals 177

### **8.3 Assembly Language Programming 177**

8.3.1 Operations and Addressing 177

8.3.2 Advanced Operations 178

8.3.3 Instruction Formats 179

### **8.4 Memory Organization and Use 180**

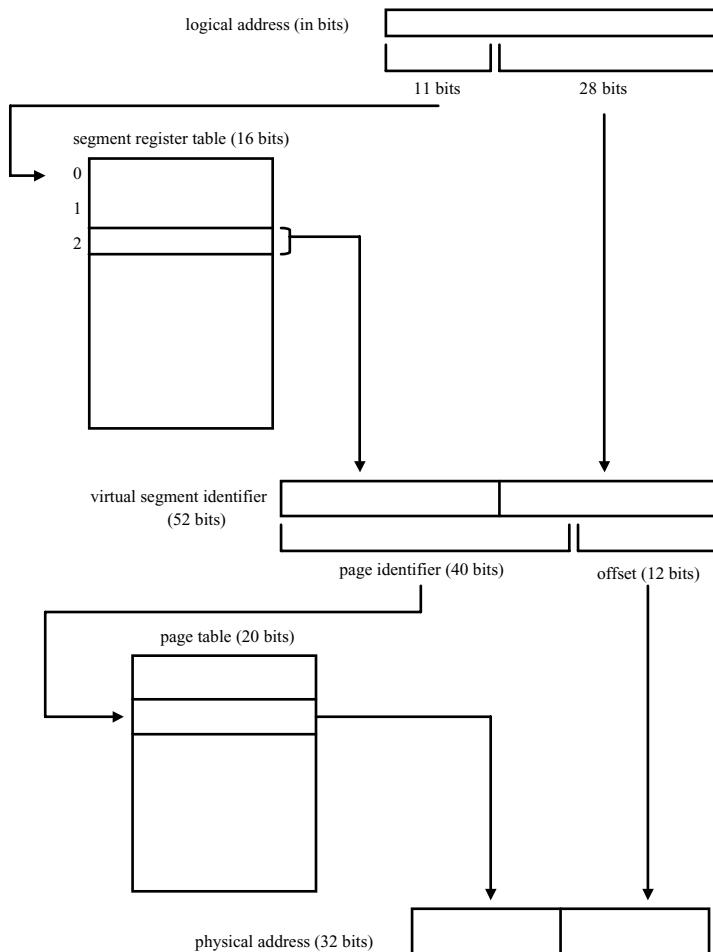

8.4.1 Memory Management 180

### **8.5 Performance Issues 180**

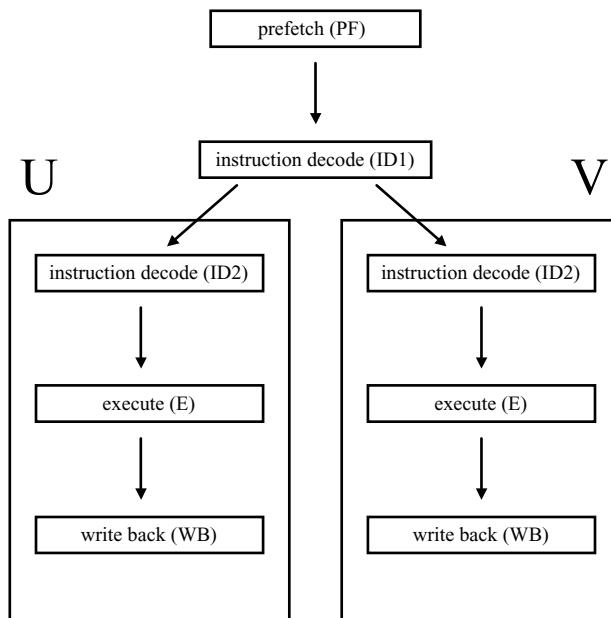

8.5.1 Pipelining 180

8.5.2 Parallel Operations 182

8.5.3 Superscalar Architecture 182

### **8.6 RISC vs. CISC Revisited 183**

### **8.7 Chapter Review 184**

### **8.8 Exercises 184**

## **9 Microcontrollers: The Atmel AVR 185**

### **9.1 Background 185**

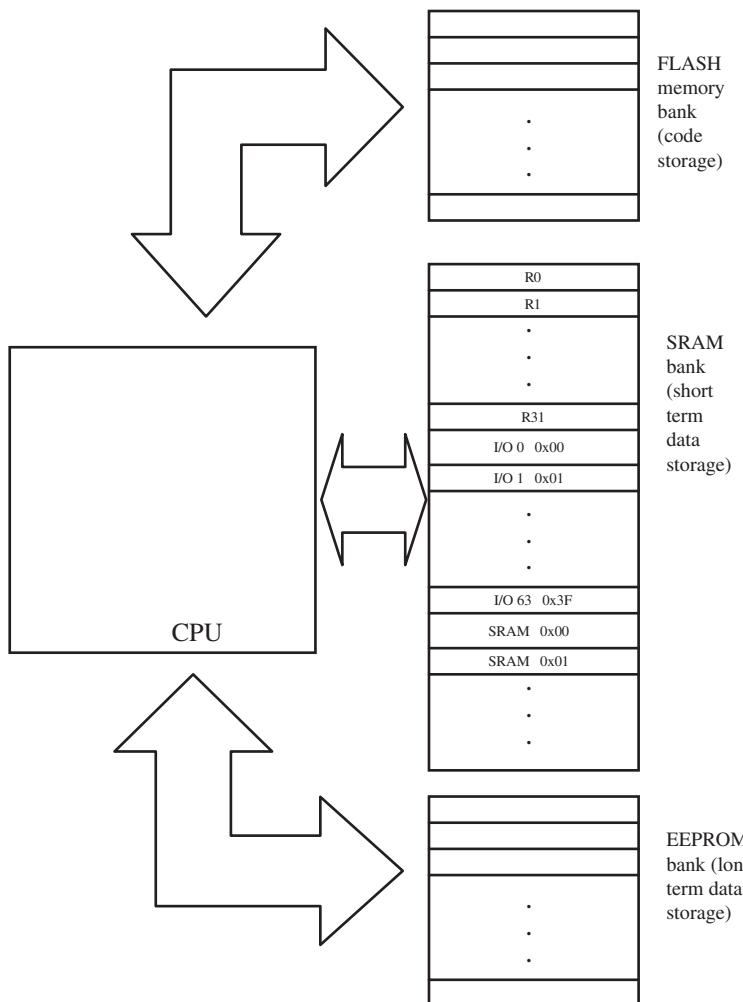

### **9.2 Organization and Architecture 186**

9.2.1 Central Processing Unit 186

9.2.2 Memory 186

9.2.3 Devices and Peripherals 191

### **9.3 Assembly Language 192**

### **9.4 Memory Organization and Use 193**

### **9.5 Issues of Interfacing 195**

9.5.1 Interfacing with External Devices 195

9.5.2 Interfacing with Timers 196

### **9.6 Designing an AVR Program 197**

### **9.7 Chapter Review 198**

### **9.8 Exercises 199**

---

# 10 Advanced Programming Topics on the JVM 200

## 10.1 Complex and Derived Types 200

- 10.1.1 The Need for Derived Types 200

- 10.1.2 An Example of a Derived Type: Arrays 201

- 10.1.3 Records: Classes Without Methods 208

## 10.2 Classes and Inheritance 210

- 10.2.1 Defining Classes 210

- 10.2.2 A Sample Class: String 212

- 10.2.3 Implementing a String 213

## 10.3 Class Operations and Methods 214

- 10.3.1 Introduction to Class Operations 214

- 10.3.2 Field Operations 214

- 10.3.3 Methods 217

- 10.3.4 A Taxonomy of Classes 221

## 10.4 Objects 223

- 10.4.1 Creating Objects as Instances of Classes 223

- 10.4.2 Destroying Objects 224

- 10.4.3 The Type Object 224

## 10.5 Class Files and .class File Structure 224

- 10.5.1 Class Files 224

- 10.5.2 Starting Up Classes 227

## 10.6 Class Hierarchy Directives 227

## 10.7 An Annotated Example: Hello, World Revisited 229

## 10.8 Input and Output: An Explanation 230

- 10.8.1 Problem Statement 230

- 10.8.2 Two Systems Contrasted 231

- 10.8.3 Example: Reading from the Keyboard in the JVM 234

- 10.8.4 Solution 235

## 10.9 Example: Factorials Via Recursion 236

- 10.9.1 Problem Statement 236

- 10.9.2 Design 236

- 10.9.3 Solution 237

## 10.10 Chapter Review 238

## 10.11 Exercises 239

## 10.12 Programming Exercises 239

**A Digital Logic 241**

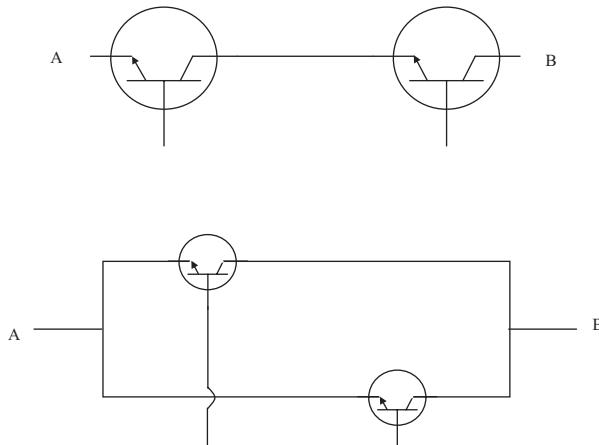

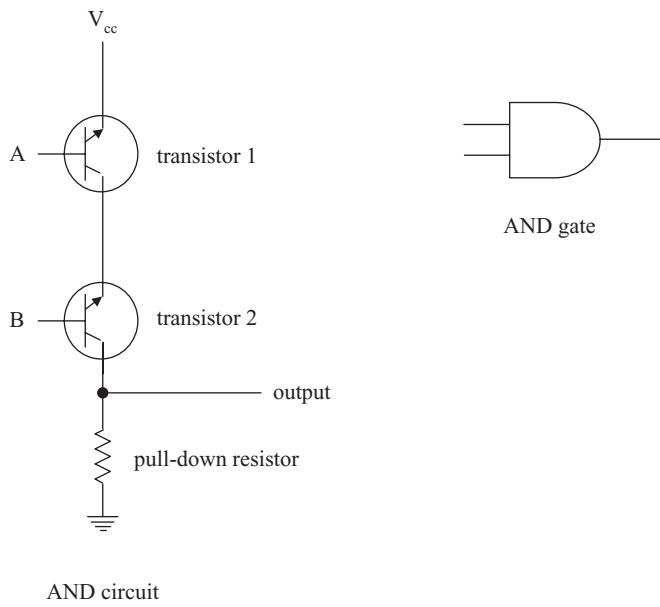

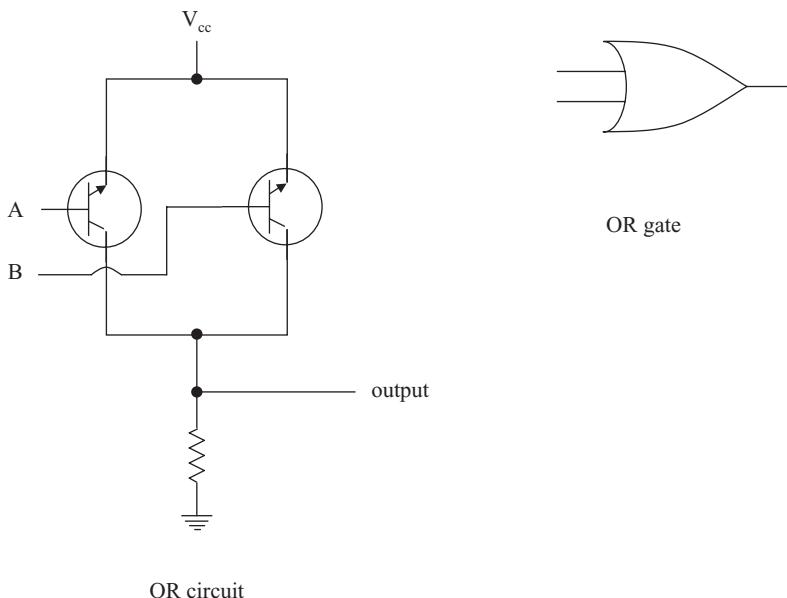

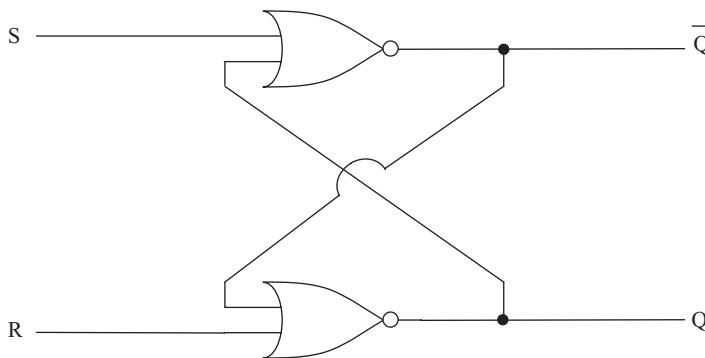

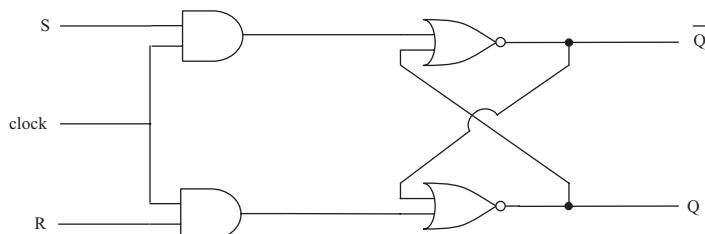

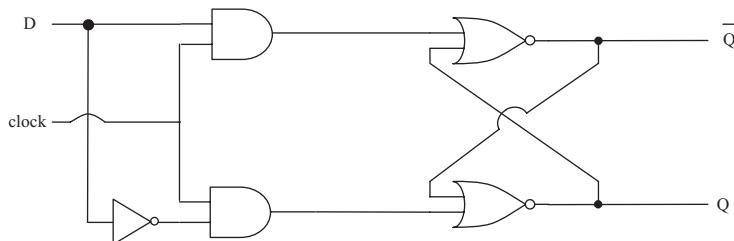

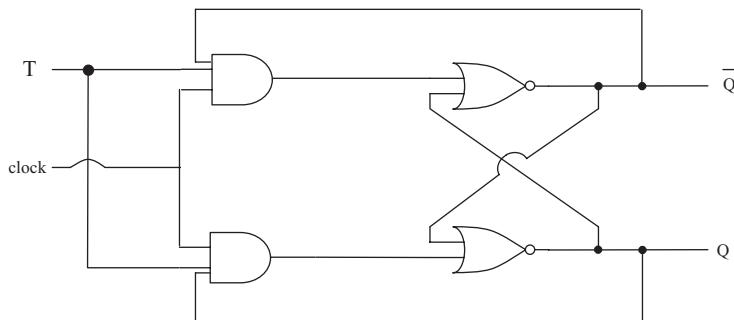

- A.1 Gates 241**

- A.2 Combinational Circuits 243**

- A.3 Sequential Circuits 245**

- A.4 Computer Operations 248**

**B JVM Instruction Set 250****C Opcode Summary by Number 281**

- C.1 Standard Opcodes 281**

- C.2 Reserved Opcodes 283**

- C.3 “Quick” Pseudo-Opcodes 283**

- C.4 Unused Opcodes 284**

**D Class File Format 285**

- D.1 Overview and Fundamentals 285**

- D.2 Subtable Structures 286**

- D.2.1 Constant Pool 286

- D.2.2 Field Table 287

- D.2.3 Methods Table 288

- D.2.4 Attributes 289

**E The ASCII Table 290**

- E.1 The Table 290**

- E.2 History and Overview 290**

**Glossary 293****Index 307**

# Preface

---

## Statement of Aims

### What

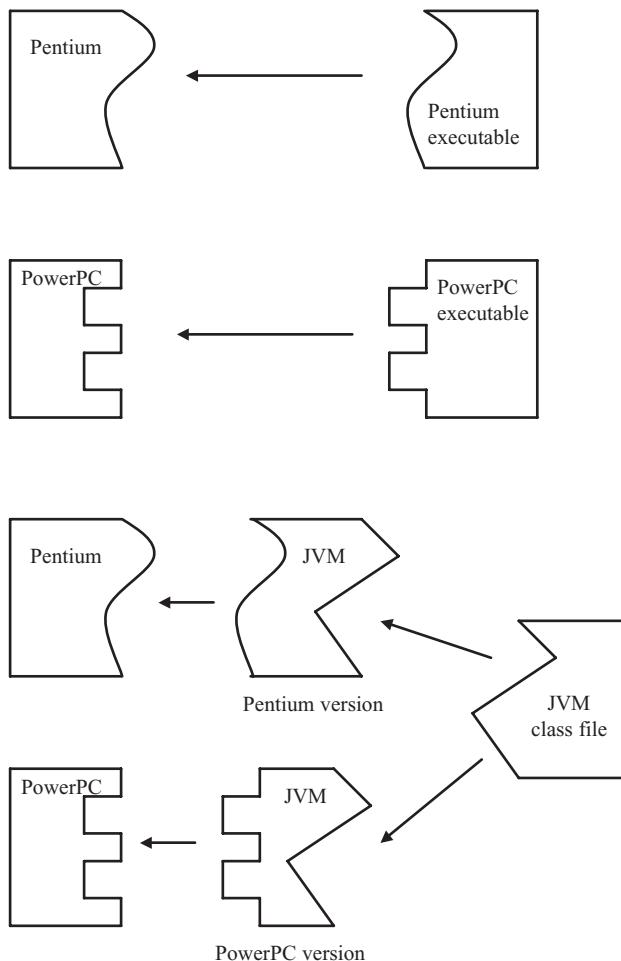

This is a book on the organization and architecture of the **Java Virtual Machine** (JVM), the software at the heart of the **Java Language** and is found inside most computers, Web browsers, PDAs, and networked accessories. It also covers general principles of machine organization and architecture, with illustrations from other popular (and not-so-popular) computers.

It is *not* a book on Java, the programming language, although some knowledge of Java or a Java-like language (C, C++, Pascal, Algol, etc.) may be helpful. Instead, it is a book about how the Java language actually causes things to happen and computations to occur.

This book got its start as an experiment in modern technology. When I started teaching at my present university (1998), the organization and architecture course focused on the 8088 running MS-DOS—essentially a programming environment as old as the sophomores taking the class. (This temporal freezing is unfortunately fairly common; when I took the same class during my undergraduate days, the computer whose architecture I studied was only two years younger than I was.) The fundamental problem is that the modern Pentium 4 chip isn't a particularly good teaching architecture; it incorporates all the functionality of the twenty-year-old 8088, including its limitations, and then provides complex workarounds. Because of this complexity issue, it is difficult to explain the workings of the Pentium 4 without detailed reference to long outdated chip sets. Textbooks have instead focused on the simpler 8088 and then have described the computers students actually use later, as an extension and an afterthought. This is analogous to learning automotive mechanics on a Ford Model A and only later discussing such important concepts as catalytic converters, automatic transmissions, and key-based ignition systems. A course in architecture should not automatically be forced to be a course in the history of computing.

Instead, I wanted to teach a course using an easy-to-understand architecture that incorporated modern principles and could itself be useful for students. Since every computer that runs a Web browser incorporates a copy of the JVM as software, almost every machine today already has a compatible JVM available to it.

This book, then, covers the central aspects of computer organization and architecture: digital logic and systems, data representation, and machine organization/architecture. It also describes the assembly-level language of one particular architecture, the JVM, with other common architectures such as the Intel Pentium 4 and the PowerPC given as supporting examples but not as the object of focus. The book is designed specifically for a standard second-year course on the architecture and organization of computers, as recommended by the IEEE Computer Society and the Association for Computing Machinery.<sup>1</sup>

---

<sup>1</sup> “Computing Curricula 2001,” December 15, 2001, Final Draft; see specifically their recommendation for course CS220.

## How

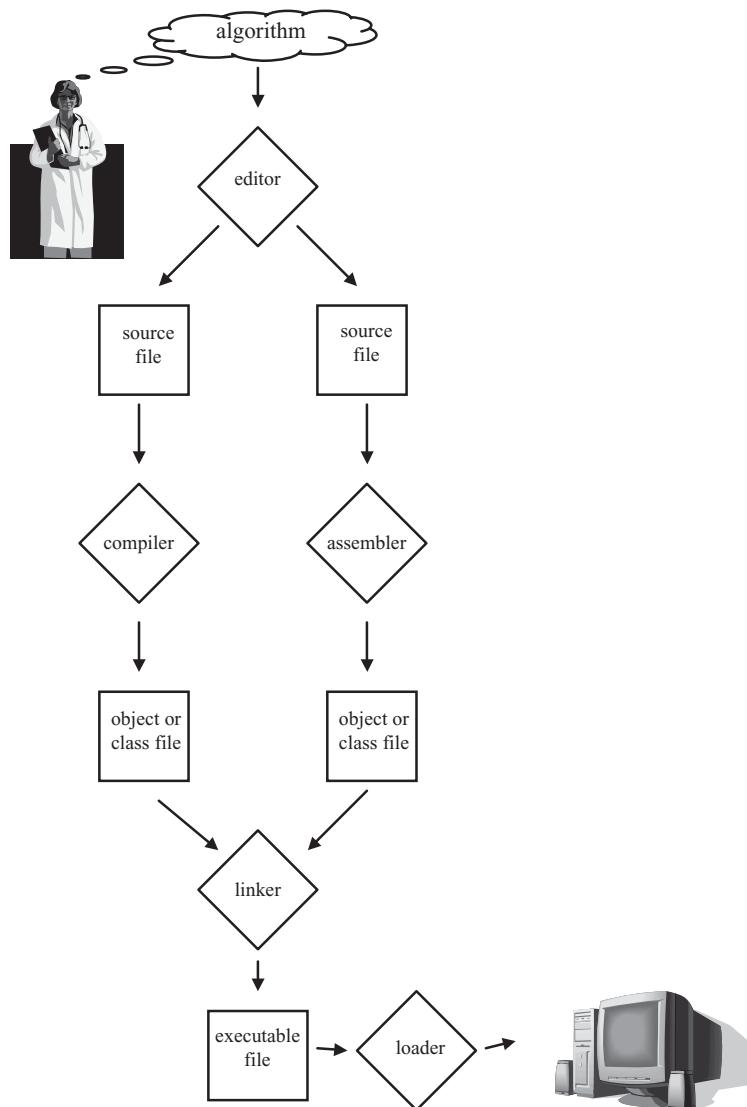

The book consists of two parts. The first half (chapters 1–5) covers general principles of computer organization and architecture and the art/science of programming in assembly language, using the JVM as an illustrative example of those principles in action (How are numbers represented in a digital computer? What does the loader do? What is involved in format conversion?), as well as the necessary specifics of JVM assembly language programming, including a detailed discussion of opcodes (What exactly does the `i2c` opcode do, and how does it change the stack? What's the command to run the assembler?). The second half of the book (chapters 6–10) focuses on specific architectural details for a variety of different CPUs, including the Pentium, its archaic and historic cousin the 8088, the Power architecture, and the Atmel AVR as an example of a typical embedded systems controller chip.

## For Whom

It is my hope and belief that this framework will permit this textbook to be used by a wide range of people and for a variety of courses. The book should successfully serve most of the software-centric community. For those primarily interested in assembly language as the basis for abstract study of computer science, the JVM provides a simple, easy-to-understand introduction to the fundamental operations of computing. As the basis for a compiler theory, programming languages, or operating systems class, the JVM is a convenient and portable platform and target architecture, more widely available than any single chip or operating system. And as the basis for further (platform-specific) study of individual machines, the JVM provides a useful explanatory teaching architecture that allows for a smooth, principled transition not only to today's Pentium, but also to other architectures that may replace, supplant, or support the Pentium in the future. For students, interested in learning how machines work, this textbook will provide information on a wide variety of platforms, enhancing their ability to use whatever machines and architectures they find in the work environment.

As noted above, the book is mainly intended for a single-semester course for second-year undergraduates. The first four chapters present core material central to the understanding of the principles of computer organization, architecture, and assembly language programming. They assume some knowledge of a high-level imperative language and familiarity with high school algebra (but not calculus). After that, professors (and students) have a certain amount of flexibility in choosing the topics, depending upon the environment and the issues. For Intel/Windows shops, the chapters on the 8088 and the Pentium are useful and relevant, while for schools with older Apples or a Motorola-based microprocessor lab, the chapter on the Power architecture is more relevant. The Atmel AVR chapter can lay the groundwork for laboratory work in an embedded systems or microcomputer laboratory, while the advanced JVM topics will be of interest to students planning on implementing JVM-based systems or on writing system software (compilers, interpreters, and so forth) based on the JVM architecture. A fast-paced class might even be able to cover all topics. The appendices are provided primarily for reference, since I believe that a good textbook should be useful even after the class is over.

# Acknowledgments

---

Without the students at Duquesne University, and particularly my guinea pigs from the Computer Organization and Assembly Language classes, this textbook couldn't have happened. I am also grateful for the support provided by my department, college, and university, and particularly for the support funding from the Philip H. and Betty L. Wimmer Family Foundation. I would also like to thank my readers, especially Erik Lindsley of the University of Pittsburgh, for their helpful comments on early drafts.

Without a publisher, this book would never have seen daylight; I would therefore like to acknowledge my editors, Tracey Dunkelberger and Kate Hargett, and through them the Prentice Hall publishing group. I would like to express my appreciation to all of the reviewers: Mike Litman, Western Illinois University; Noe Lopez Benitez, Texas Tech University; Larry Morell, Arkansas Tech University; Peter Smith, California State University–Channel Islands; John Sigle, Louisiana State University–Shreveport; and Harry Tyrer, University of Missouri–Columbia. Similarly, without the software, this book wouldn't exist. Aside from the obvious debt of gratitude to the people at Sun who invented Java, I specifically would like to thank and acknowledge Jon Meyer, the author of `jasmin`, both for his software and for his helpful support.

Finally, I would like to thank my wife, Jodi, who drew preliminary sketches for most of the illustrations and, more importantly, has managed to put up with me throughout the book's long gestation and is still willing to live in the same house.

*This page intentionally left blank*

---

# Part the First: Imaginary Computers

*This page intentionally left blank*

---

# Computation and Representation

## 1.1 Computation

A computer

Also a computer

### 1.1.1 Electronic Devices

How many people really know what a computer is? If you asked, most people would point to a set of boxes on someone's desk (or perhaps in someone's briefcase)—probably a set of dull-looking rectangular boxes encased in gray or beige plastic, and surrounded by a tangle of wires and perhaps something resembling a TV. If pressed for detail, they would point at one particular box as “the computer.” But, of course, there are also computers hidden in all sorts of everyday electronic gadgets to make sure that your car's fuel efficiency stays high enough, to interpret the signals from a DVD player, and possibly even to make sure your morning toast is the right shade of brown. To most people, though, a computer is still the box you buy at an electronics shop, with bits and bytes and gigahertz that are often compared, but rarely understood.

In functional terms, a computer is simply a high-speed calculator capable of performing thousands, millions, or even billions of simple arithmetic operations per second from a stored program. Every thousandth of a second or so, the computer in your car reads a few key performance indicators from various sensors in the engine and adjusts the machine slightly to ensure proper functioning. The key to being of any use is at least partially in the sensors. The computer itself processes only electronic signals. The sensors are responsible for determining what's really going on under the hood and converting that into a set of electronic signals that describe, or represent, the current state of the engine. Similarly, the adjustments that the computer makes are stored as electronic signals and converted back into physical changes in the engine's working.

How can electronic signals “represent” information? And how exactly does a computer process these signals to achieve fine control without any physical moving parts or representation? Questions of representation such as these are, ultimately, the key to understanding both how computers work and how they can be deployed in the physical world.

### 1.1.2 Algorithmic Machines

The single most important concept in the operation of a computer is the idea of an **algorithm**: an unambiguous, step-by-step process for solving a problem or achieving a desired end. The ultimate definition of a computer does not rely on its physical properties, or even on its electrical properties (such as its transistors), but on its ability to represent and carry out algorithms from a stored program. Within the computer are millions of tiny circuits, each of which performs a specific well-defined task (such as adding two integers together or causing an individual wire or set of wires to become energized) when called upon. Most people who use or program computers are not aware of the detailed workings of these circuits.

In particular, there are several basic types of operations that a typical computer can perform. As computers are, fundamentally, merely calculating machines, almost all of the functions they can perform are related to numbers (and concepts representable by numbers). A computer can usually perform basic mathematical operations such as addition and division. It can also perform basic comparisons—is one number equal to another number? Is the first number less than the second? It can store millions or billions of pieces of information and retrieve them individually. Finally, it can adjust its actions based on the information retrieved and the comparisons performed. If the retrieved value is greater than the previous value, then (for example) the engine is running too hot, and a signal should be sent to adjust its performance.

### 1.1.3 Functional Components

#### *System-Level Description*

Almost any college bulletin board has a few ads that read something like “GREAT MACHINE! 3.0-GHz Intel Celeron D, 512 mg, 80-GB hard drive, 15-inch monitor, must sell to make car payment!” Like most ads, there’s a fair bit of information in there that requires extensive unpacking to understand fully. For example, what part of a 15-inch monitor is actually 15 inches? (The length of the diagonal of the visible screen, oddly enough.) In order to understand the detailed workings of a computer, we must first understand the major components and their relations to each other (figure 1.1).

**Figure 1.1** Major hardware components of a computer

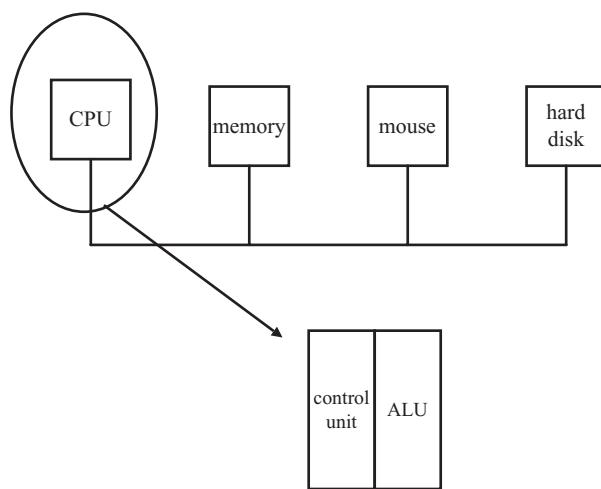

### *Central Processing Unit*

The heart of any computer is the **Central Processing Unit**, or CPU. This is usually a single piece of high-density circuitry built on single **integrated circuit** (IC) silicon chip (figure 1.2). Physically, it usually looks like a small piece of silicon, mounted on a plastic slab a few centimeters square, surrounded by metal pins. The plastic slab itself is mounted on the **motherboard**, an electronic circuit board consisting of a piece of plastic and metal tens of centimeters

**Figure 1.2** Photograph of a CPU chip

on a side, containing the CPU and a few other components that need to be placed near the CPU for speed and convenience. Electronically, the CPU is the ultimate controller of the computer, as well as the place where all calculations are performed. And, of course, it's the part of the computer that everyone talks and writes about—a 3.60-GHz Pentium 4 computer, like the Hewlett-Packard HP xw4200, is simply a computer whose CPU is a Pentium 4 chip and that runs at a speed of 3.60 gigahertz (GHz), or 3,600,000,000 **machine cycles** per second. Most of the basic operations a computer can perform take one machine cycle each, so another way of describing this is to say that a 3.60-GHz computer can perform just over 3.5 billion basic operations per second. At the time of writing, 3.60 GHz is a fast machine, but this changes very quickly with technological developments. For example, in 2000, a 1.0-GHz Pentium was the state of the art, and, in keeping with a long-standing rule of thumb (Moore's law) that computing power doubles every 18 months, one can predict the wide availability of 8-GHz CPUs by 2008.

## S I D E B A R

### Moore's Law

Gordon Moore, the cofounder of Intel, observed in 1965 that the number of transistors that could be put on a chip was doubling every year. In the 1970s, that pace slowed slightly, to a doubling every 18 months, but has been remarkably uniform since then, to the surprise of almost everyone, including Dr. Moore himself. Only in the past few years has the pace weakened.

The implications of smaller transistors (and increasing transistor density) are profound. First, the cost per square inch of a silicon chip itself has been relatively steady by comparison, so doubling the density will approximately halve the cost of a chip. Second, smaller transistors react faster, and components can be placed closer together, so that they can communicate with each other faster, vastly increasing the speed of the chip. Smaller transistors also consume less power, meaning longer battery life and lower cooling requirements, avoiding the need for climate-controlled rooms and bulky fans. Because more transistors can be placed on a chip, less soldering is needed to connect chips together, with an accordingly reduced chance of solder breakage and correspondingly greater overall reliability. Finally, the fact that the chips are smaller means that computers themselves can be made smaller, enough to make things like embedded controller chips and/or personal digital assistants (PDAs) practical. It is hard to overestimate the effect that Moore's law has had on the development of the modern computer. Moore's law by now is generally taken to mean, more simply, that the power of an available computer doubles every 18 months (for whatever reason, not just transistor density). A standard, even low-end, computer available off the shelf at the local store is faster, more reliable, and has more memory than the original Cray-1 supercomputer of 1973.

The problem with Moore's law is that it will not hold forever. Eventually, the laws of physics are likely to dictate that a transistor can't be any smaller than an atom (or something like that). More worrisome is what's sometimes called Moore's second law, which states that fabrication costs double every three years. As long as fabrication costs grow more slowly than computer power, the performance/cost ratio should remain reasonable. But the cost of investing in new chip technologies may make it difficult for manufacturers such as Intel to continue investing in new capital.

CPUs can usually be described in families of technological progress; the Pentium 4, for example, is a further development of the Pentium, the Pentium II, and the Pentium III, all manufactured by the Intel corporation. Before that, the Pentium itself derived from a long line of numbered Intel chips, starting with the Intel 8088 and progressing through the 80286, 80386, and 80486. The so-called “x86 series” became the basis for the best-selling IBM personal computers (PCs and their clones) and is probably the most widely used CPU chip. Modern Apple computers use a different family of chips, the PowerPC G3 and G4, manufactured by a consortium of Apple, IBM, and Motorola (AIM). Older Apples and Sun workstations used chips from the Motorola-designed 68000 family.

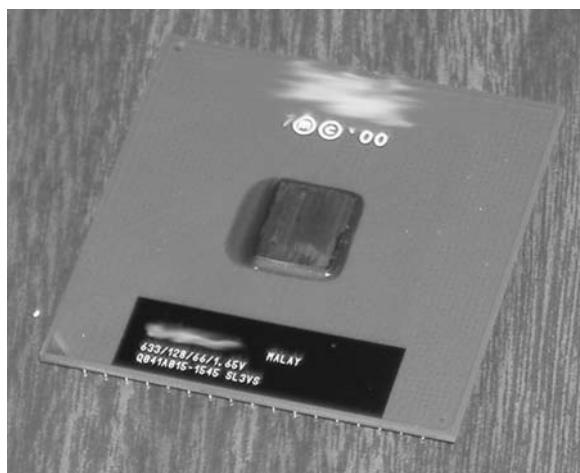

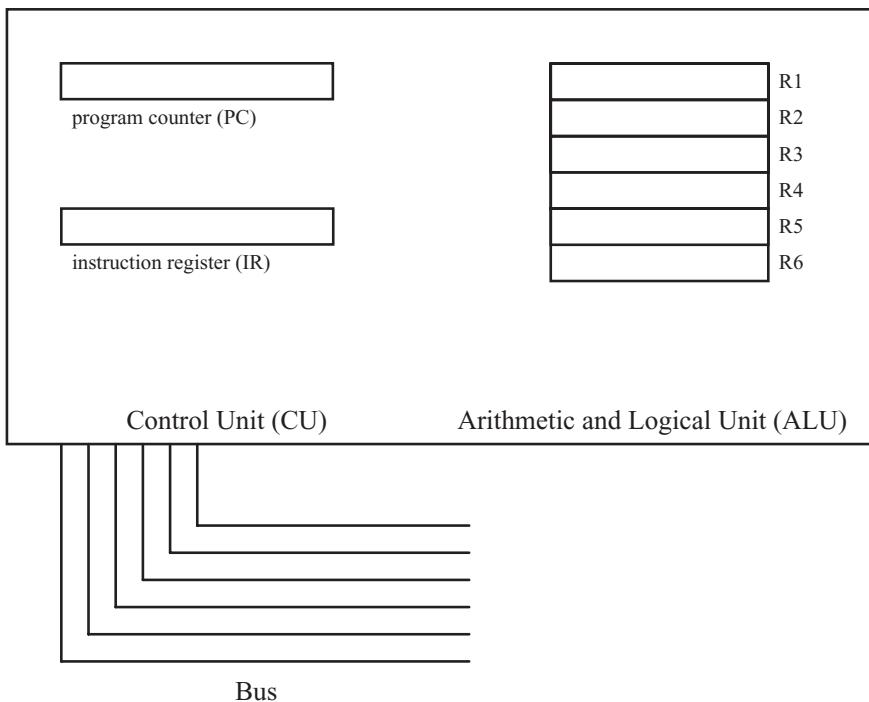

The CPU itself can be divided into two or three main functional components. The **Control Unit** is responsible for moving data around within the machine. For example, the Control Unit takes care of loading individual program instructions from memory, identifying individual instructions, and passing the instructions to other appropriate parts of the computer to be performed. The **Arithmetic and Logical Unit** (ALU) performs all necessary arithmetic for the computer; it typically contains special-purpose hardware for addition, multiplication, division, and so forth. It also, as the name implies, performs all the logical operations, determining whether a given number is bigger or smaller than another number or checking whether two numbers are equal. Some computers, particularly older ones, have special-purpose hardware, sometimes on a separate chip from the CPU itself, to handle operations involving fractions and decimals. This special hardware is often called the **Floating Point Unit** or FPU (also called the Floating Point Processor or FPP). Other computers fold the FPU hardware onto the same CPU chip as the ALU and the Control Unit, but the FPU can still be thought of as a different module within the same set of circuitry.

### *Memory*

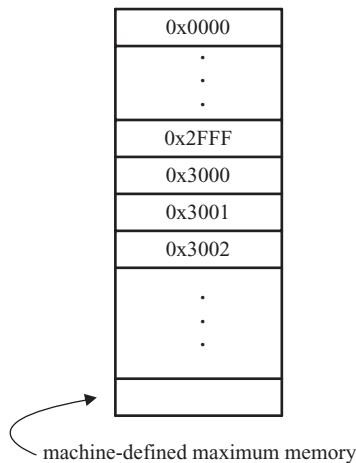

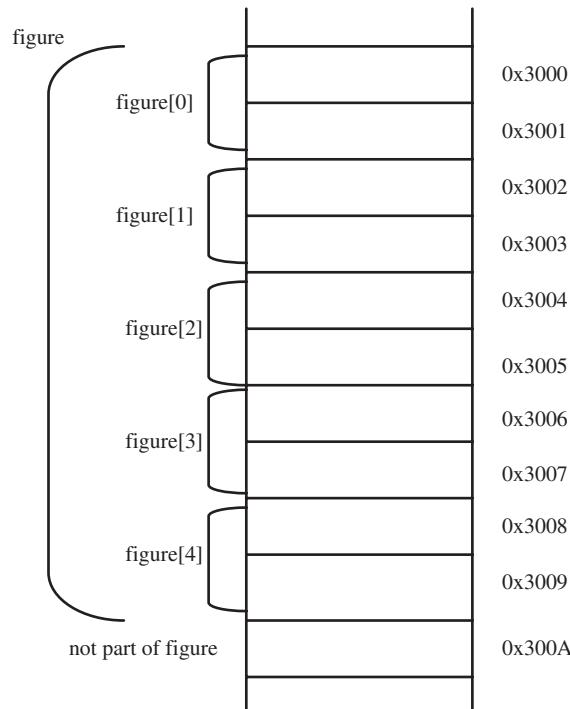

Both the program to be executed and its data are stored in memory. Conceptually, memory can be regarded as a very long array or row of electromagnetic storage devices. These array locations are numbered, from 0 to a CPU-defined maximum, and can be addressed individually by the Control Unit to place data memory or to retrieve data from memory (figure 1.3). In addition, most modern machines allow high-speed devices such as disk drives to copy large blocks of data without needing the intervention of the Control Unit for each signal. Memory can be broadly divided into two types: **Read-Only Memory** (ROM), which is permanent, unalterable, and remains even after the power is switched off, and **Random Access Memory** (RAM), the contents of which can be changed by the CPU for temporary storage but usually disappears when the power does. Many machines have both kinds of memory; ROM holds standardized data and a basic version of the operating system that can be used to start the machine. More extensive programs are held in long-term storage such as disk drives and CDs, and loaded as needed into RAM for short-term storage and execution.

This simplified description deliberately hides some tricky aspects of memory that the hardware and operating system usually take care of for the user. (These issues also tend to be hardware-specific, so they will be dealt with in more detail in later chapters.) For example, different computers, even with identical CPUs, often have different amounts of memory. The amount of physical memory installed on a computer may be less than the maximum number of locations the CPU can address or, in odd cases, may even be more. Furthermore, memory located on the CPU chip

**Figure I.3** Block diagram of a linear array of memory cells

itself can typically be accessed much more quickly than memory located on separate chips, so a clever system can try to make sure that data is moved or copied as necessary to be available in the fastest memory when needed.

#### *Input/Output (I/O) Peripherals*

In addition to the CPU and memory, a computer usually contains other devices to read, display or store data, or more generally to interact with the outside world. These devices vary from commonplace keyboards and hard drives through more unusual devices like facsimile (FAX) boards, speakers, and musical keyboards to downright weird gadgets like chemical sensors, robotic arms, and security deadbolts. The general term for these gizmos is **peripherals**. For the most part, these devices have little direct effect on the architecture and organization of the computer itself; they are just sources and sinks for information. A keyboard, for instance, is simply a device to let the computer gather information from the user. From the point of view of the CPU designer, data is data, whether it came from the Internet, from the keyboard, or from a fancy chemical spectrum analyzer.

In many cases, a peripheral can be physically divided into two or more parts. For example, computers usually display their information to the user on some form of video monitor. The **monitor** itself is a separate device, connected via a cable to a video adapter board located inside the computer's casing. The CPU can draw pictures by sending command signals to the video board, which in turn will generate the picture and send appropriate visual signals over the video cable to the monitor itself. A similar process describes how the computer can load a file from many different kinds of hard drives via a SCSI (Small Computer System Interface) controller card, or interact via an Ethernet card with the millions of miles of wire that comprise the Internet. Conceptually, engineers draw a distinction between the device itself, the device cable (which is often just a wire), and the device controller, which is usually a board inside the computer—but to the programmer, they're usually all one device. Using this kind of logic, the entire Internet, with

its millions of miles of wire, is just “a device.” With a suitably well-designed system, there’s not much difference between downloading a file off the Internet or loading it from a hard drive.

### *Interconnections and Buses*

In order for the data to move between the CPU, memory, and the peripherals, there must be connections. These connections, especially between separate boards, are usually groups of wires to allow multiple individual signals to be sent in a block. The original IBM-PC, for example, had eight wires to allow data to pass between the CPU and peripherals. A more modern computer’s PCI (Peripheral Component Interconnect) bus has 64 data wires, allowing data to pass eight times as fast, even before increased computer speed is taken into account. These wires are usually grouped into what is called a **bus**, a single wire set connecting several different devices. Because it is shared (like an early party-line telephone), only one device can transmit data at a time, but the data is available to any connected device. Additional wires are used to determine which device should listen to the data and what exactly it should do when it gets it.

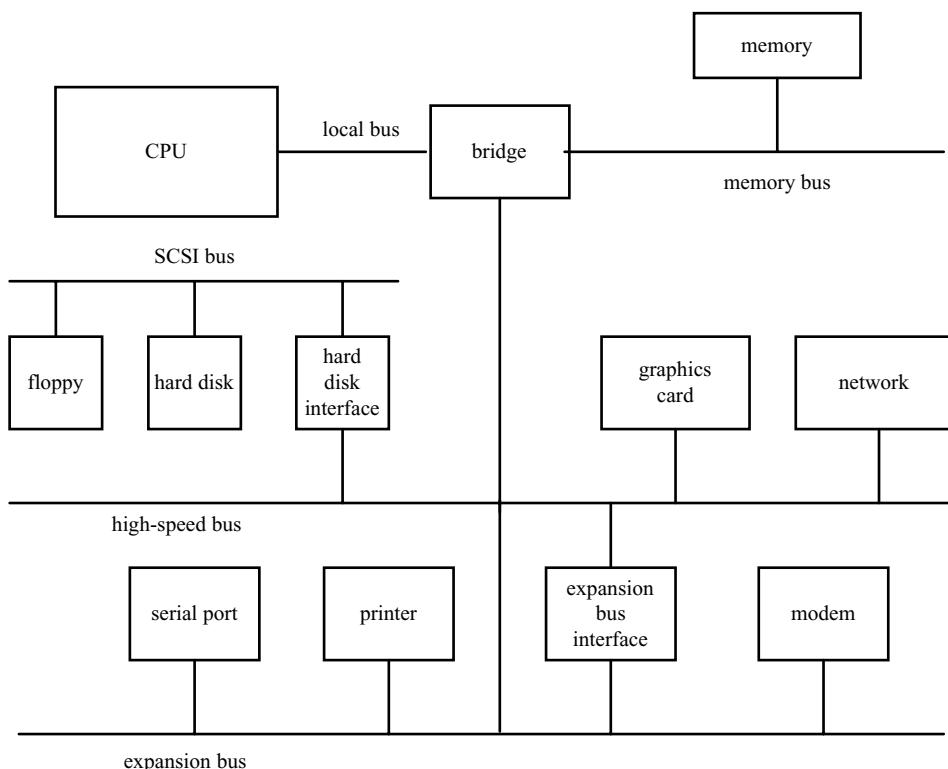

In general, the more devices attached to a single bus, the slower it runs. This is true for two main reasons. First, the more devices, the greater the possibility that two devices will have data to transmit at the same time, and thus that one device will have to wait its turn. Second, more devices usually means longer wires in the bus, which reduces the speed of the bus due to delays in propagation—the time it takes a signal to get from one end of the wire to the other. For this reason, many computers now have a multiple-bus design, in which, for example, the local bus connects the CPU with high-speed memory stored on the CPU’s motherboard (often on the CPU chip itself). The system bus connects the memory board, the CPU motherboard, and an “expansion bus” interface board. The expansion bus, in turn, is a second bus that connects to other devices such as the network, the disk drives, the keyboard, and the mouse.

On particularly high-performance computers (such as the one in figure 1.4), there may be four or five separate buses, with one reserved for high-speed, data-intensive devices such as the network and video cards, while lower-speed devices such as the keyboard are relegated to a separate, slower bus.

### *Support Units*

In addition to the devices mentioned already, a typical computer will have a number of components that are important to its physical condition. For example, inside the case (itself crucial for the physical protection of the delicate circuit boards) will be a power supply that converts the AC line voltage into an appropriately conditioned DC voltage for the circuit boards. There may also be a battery, particularly in laptops, to provide power when wall current is unavailable and to maintain memory settings. There is usually a fan to circulate air inside the case and to prevent components from overheating. There may also be other devices such as heat sensors (to control fan speed), security devices to prevent unauthorized use or removal, and often several wholly internal peripherals such as internal disk drives and CD readers.

## **1.2 Digital and Numeric Representations**

### **1.2.1 Digital Representations and Bits**

At a fundamental level, computer components, like so many other electronic components, have two stable states. Lights are on or off, switches are open or closed, and wires are either carrying current or not. In the case of computer hardware, individual components such as transistors and

**Figure 1.4** Block architecture of a high-speed, multibus computer

resistors are either at 0 volts relative to ground or at some other voltage (typically 5 volts above ground). These two states are usually held to represent the numbers 1 and 0, respectively. In the early stages of computer development, these values were hand-encoded by flipping mechanical switches. Today, high-speed transistors serve much the same purpose, but the representation of data in terms of these two values remains unchanged since the 1940s. Every such 1 or 0 is usually called a **bit**, an abbreviation for “binary digit.” (Of course, the word “bit” is itself a normal English word, meaning “a very small amount”—which also describes a “bit” of information.)

### S I D E B A R

#### How Transistors Work

The single most important electrical component in the modern computer is the transistor, first invented by Bardeen, Brattain, and Shockley in 1947 at Bell Telephone Labs. (These men received the Nobel Prize for Physics in 1956 for this invention.) The fundamental idea involves some fairly high-powered (well, yes, Nobel-caliber) quantum physics, but it can be understood in terms of electron transport, as long as you don’t need the actual equations. A transistor consists mostly of a type of material called a **semiconductor**, which occupies an uneasy middle ground between

good conductors (like copper) and bad conductors/good insulators (like glass). A key aspect of semiconductors is that their ability to transmit electricity can change dramatically with impurities (**dopants**) in the semiconductor.

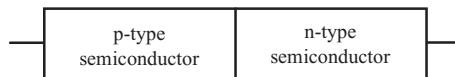

For example, the element phosphorus, when added to pure silicon (a semiconductor), will donate electrons to the silicon. Since electrons have a negative charge, phosphorus is termed an **n-type** dopant, and phosphorus-doped silicon is sometimes called an **n-type semiconductor**. Aluminum, by contrast, is a **p-type** dopant and will actually remove—actually, lock up—electrons from the silicon matrix. The places where these electrons have been removed are sometimes called “holes” in the p-type semiconductor.

When you put a piece of n-type next to a piece of p-type semiconductor (the resulting widget is called a **diode**; figure 1.5), an interesting electrical effect occurs. An electrical current will not typically be able to pass through such a diode; the electrons carrying the current will encounter and “fall into” the holes. If you apply a **bias voltage** to this gadget, however, the extra electrons will fill the holes, allowing current to pass. This means that electricity can pass in only one direction through a diode, which makes it useful as an electrical **rectifier**.

Structure of diode

Symbol for diode

**Figure 1.5** Diodes

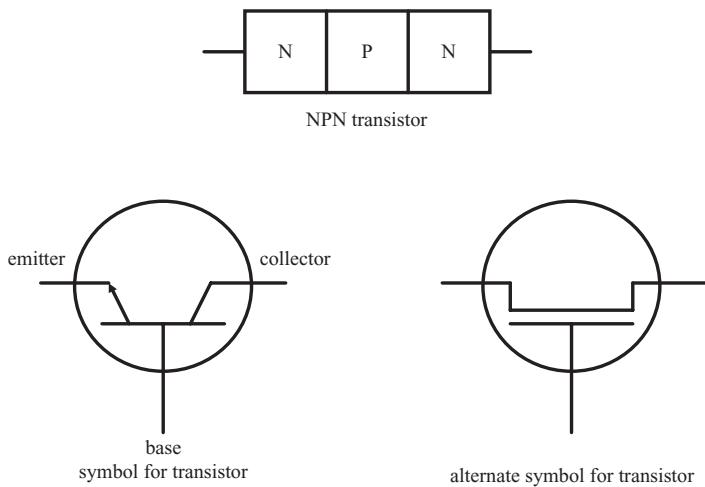

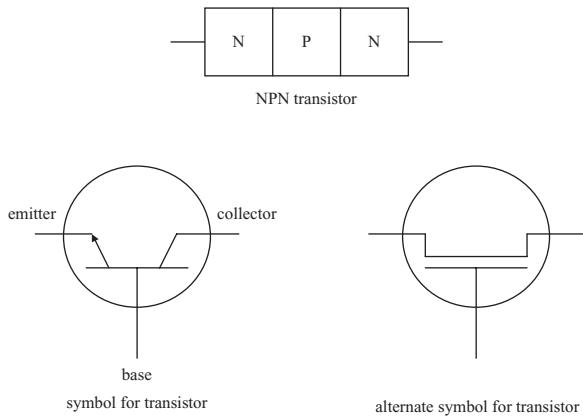

A modern transistor is made like a semiconductor sandwich; a thin layer of p-type semiconductor between two slices of n-type semiconductor, or sometimes the reverse. (Yes, this is just two diodes back to back; figure 1.6). Under normal circumstances, current can't pass from the **emitter** to the **collector** as electrons fall into the holes. Applying a **bias voltage** to the **base** (the middle wire) will fill the holes so that electricity can pass. You can think of the base as a gate that can open or shut to allow electricity to flow or not. Alternatively, you can think of it as a valve in a hosepipe to control the amount of water it lets through. Turn it one way, and the electrical signal drops to a trickle. Turn it the other way, and it flows without hindrance.

The overall effect of the transistor is that a small change in voltage (at the base) will result in a very large change in the amount of current that flows from the emitter to the collector. This makes a transistor extremely useful for amplifying small signals. It also can function as a binary switch, the key advantage being that it has no moving parts and thus nothing to break. (It's also much, much faster to throw an electrical switch than a mechanical one.) With the invention of the IC, for which Jack Kilby also won the Nobel Prize, engineers gained the ability to create thousands, millions, or billions of tiny transistors by doping very small areas of a larger piece of silicon. To this day, this remains the primary way that computers are manufactured.

(continued)

**Figure 1.6** Transistors

### 1.2.2 Boolean Logic

Modern computers operate using a logic based on **bits**. A bit is the smallest unit that can be said to carry information, as in the children's game "Twenty Questions," where each yes or no question yields an answer that could be encoded with a single bit (for example, 1 represents a "yes" and 0 a "no"). If you are familiar with the old Milton Bradley board game, "Guess Who," the same principle applies. By asking yes/no questions, you gradually learn which person your opponent has chosen—and by recording the answers to your questions, you can recreate that learning at any point. A bit is therefore the smallest unit that can be operated upon—stored, transmitted, or manipulated—using logic. The conventional way of performing logic on bit quantities is called **Boolean** logic, after the nineteenth-century mathematician George Boole. He identified three basic operations—AND, OR, and NOT—and defined their meaning in terms of simple changes on bits. For example, the expression X AND Y is true (a "yes," or a 1) if and only if, independently, X is a "yes" and Y is a "yes." The expression X OR Y, conversely, is a "yes" if either X is a "yes" or Y is a "yes." An equivalent way of stating this is that X OR Y is false (a "no," or a 0) if and only if X is a "no" and Y is a "no." The expression NOT X is the exact opposite of X: "yes" if X is a "no" and "no" if X is a "yes" (figure 1.7). Because a bit can be in only one of two states, there are no other possibilities to consider. These operations (AND, OR, and NOT) can be nested or combined as needed. For example, NOT (NOT X) is the exact opposite of the exact opposite of X, which works out to be the same as X itself. These three operations parallel their English lexical equivalents fairly well: if I want a cup of coffee "with milk and sugar," logically what I am asking for is a cup of coffee where "with milk" is true AND "with sugar" is true. Similarly, a cup of coffee "without milk or sugar" is the same as a cup "with no milk and no sugar." (Think about it for a bit.)

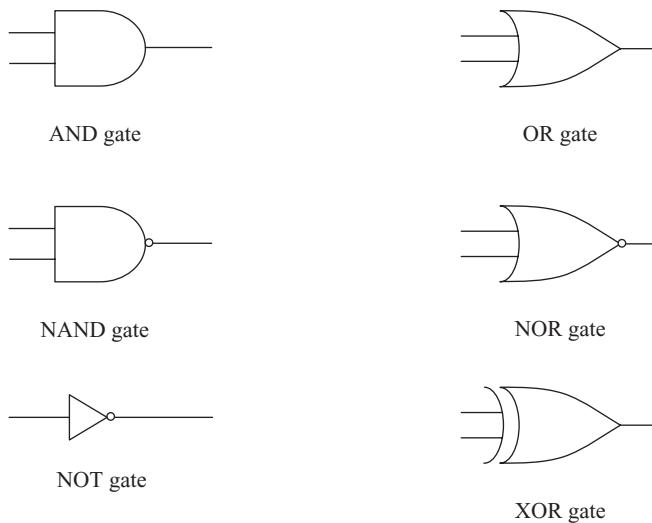

In addition to these three basic operations, there are a number of other operations that can be defined from them. For example, NAND is an abbreviation for NOT-AND. The expression

| AND | no | yes | OR  | no  | yes | NOT |     |

|-----|----|-----|-----|-----|-----|-----|-----|

| no  | no | no  | no  | no  | yes | no  | yes |

| yes | no | yes | yes | yes | yes | yes | no  |

**Figure 1.7** Truth tables for AND, OR, and NOT

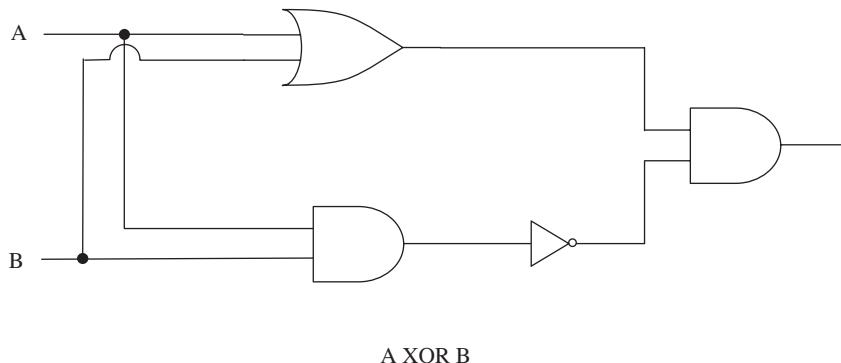

$X \text{ NAND } Y$  refers to  $\text{NOT}(X \text{ AND } Y)$ . Similarly,  $X \text{ NOR } Y$  refers to  $\text{NOT}(X \text{ OR } Y)$ . Another common expression is exclusive-OR, written  $\text{XOR}$ . The expression  $X \text{ OR } Y$  is true if  $X$  is true,  $Y$  is true, or both. By contrast,  $X \text{ XOR } Y$  is true if  $X$  is true or  $Y$  is true, but not both. This difference is not captured cleanly in English but is implicit in several different uses: for example, if I am asked if I want milk or sugar in my coffee, I'm allowed to say "yes, please," meaning that I want both. This is the normal (inclusive) OR. By contrast, if I am offered coffee or tea, it wouldn't make much sense for me to say "yes," meaning both. This is an exclusive XOR; I can have either coffee XOR tea, but not both at the same time.

From a strictly theoretical point of view, it doesn't matter much whether 1/"yes"/"true" is encoded as ground voltage or as 5 volts above ground as long as 0/"no"/"false" is encoded differently and the difference is consistently applied. From the point of view of a computer engineer or system designer, there may be particular reasons (such as power consumption) to choose one representation over another. The choice of representation can have profound implications for the design of the chips themselves. The Boolean operations described above are usually implemented in hardware at a very low level on the chip itself. For example, one can build a simple circuit with a pair of switches (or transistors) that will allow current to flow only if both switches are closed. Such a circuit is called an AND gate, because it implements the AND function on the 2 bits represented by the switch state. This tiny circuit and others like it (OR gates, NAND gates, and so forth), copied millions or billions of times across the computer chip, are the fundamental building blocks of a computer. (See Appendix A for more on how these blocks work.)

### 1.2.3 Bytes and Words

For convenience, 8 bits are usually grouped into a single block, conventionally called a **byte**. There are two main advantages to doing this. First, writing and reading a long sequence of 0s and 1s is, for humans, tedious and error prone. Second, most interesting computations require more data than a single bit. If multiple wires are available, as in standard buses, then electrical signals can be moved around in groups, resulting in faster computation.

The next-largest named block of bits is a **word**. The definition and size of a word are not absolute, but vary from computer to computer. A word is the size of the most convenient block of data for the computer to deal with. (Usually, though not always, it's the size of the bus leading to main memory—but see the Intel 8088, discussed later, for a counterexample.) For example, the Zilog Z-80 microprocessor (the chip underlying the Radio Shack TRS-80, popular in the mid-1970s) had a word size of 8 bits, or 1 byte. The CPU, memory storage, and buses had all been optimized to handle 8 bits at a time (for example, there were eight data wires in the system bus). In the event that the computer had to process 16 bits of data, it would be handled in two separate halves, while if the computer had only 4 bits of data to process, the CPU would work as though it had 8 bits of data, then throw away the extra 4 (useless) bits. The original IBM-PC, based on the

Intel 8088 chip, had a word size of 16 bits. More modern computers such as the Intel Pentium 4 or the PowerPC G4 have word sizes of 32 bits, and computers with word sizes of 64 bits or even larger, such as the Intel Itanium and AMD Opteron series, are available. Especially for high-end scientific computation or graphics, such as in home video game consoles, a large word size can be key to delivering data fast enough to allow smoothly animated, high-detail graphics.

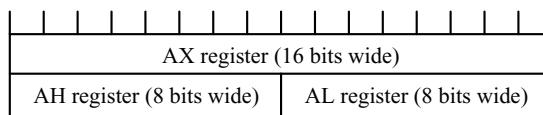

Formally speaking, the word size of a machine is defined as the size (in bits) of the machine's **registers**. A register is the memory location inside the CPU where the actual computations, such as addition, subtraction, and comparisons, take place (figure 1.8). The number, type, and organization of registers vary widely from chip to chip and may even change significantly within chips of the same family. The Intel 8088, for example, had four 16-bit general-purpose registers, while the Intel 80386, designed seven years later, used 32-bit registers instead. Efficient use of registers is key to writing fast, well-optimized programs. Unfortunately, because of the differences between different computers, this can be one of the more difficult aspects of writing such programs for various computers.

**Figure 1.8** Typical internal structure of a CPU

#### 1.2.4 Representations

##### *Bit Patterns are Arbitrary*

Consider, for a moment, one of the registers in an old-fashioned 8-bit microcomputer chip. How many different patterns can it hold? Other ways of asking the same question are to consider how

many different ways you can arrange a sequence of 10 pennies in terms of heads and tails or how many strings can be made up of only 8 letters, each of which is a 0 or a 1.

There are two possibilities for the first bit/coin/letter/digit, two for the second, and so on until we reach the eighth and final digit. There are thus  $2 \cdot 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2 \cdot 2$  possibilities. This works out to  $2^8$  or 256 different storable patterns. Similar reasoning shows that there are  $2^{32}$  or just over 4 billion storable patterns in a 32-bit register. (All right, for the pedants,  $2^{32} = 4,294,967,296$ . A handy rule of thumb for dealing with large binary powers is that  $2^{10}$ , really 1024, is close to 1000. Remember that to multiply numbers, you add the exponents:  $a^b \cdot a^c = a^{b+c}$ . Thus,  $2^{32} = 2^{2+10+10+10}$ , or  $2^2 \cdot 2^{10} \cdot 2^{10}$ , or about  $4 \cdot 1000 \cdot 1000 \cdot 1000$ .)

Yes, but what do these patterns mean? The practical answer is: whatever you as the programmer want them to mean. As you'll see in the next subsection, it's fairly easy to read the bit pattern 00101101 as the number 77. It's also possible to read it as a record of the answers to eight different yes/no questions. ("Are you married?"—No. "Are you older than 25?"—No. "Are you male?"—Yes. And so forth.) It could also represent a key being pressed on the keyboard (in this case, the pattern represents the ASCII value for a capital M). The interpretation of bit patterns is arbitrary, and computers can typically use the same patterns in many ways. Part of the programmer's task is to make sure that the computer interprets these arbitrary and ambiguous patterns correctly at all times.

### Natural Numbers

A common way to interpret bit patterns involves using **binary** arithmetic (in base 2). In conventional, or **decimal** (base 10) arithmetic, there are only ten different number symbols, 0 through 9. Larger numbers are expressed as individual digits times a power of the base value. The number four hundred eighty-one (481), for instance, is really  $4 \cdot 10^2 + 8 \cdot 10^1 + 1$ . Using this notation, we can express all natural numbers up to nine hundred ninety-nine in only three decimal digits. Using a similar notation, but adding up powers of 2, we can express any number in binary using only 0s and 1s.

Taking as an example the (decimal) number 85, simple arithmetic shows that it is equivalent to  $64 + 16 + 4 + 1$ , or (in more detail) to  $1 \cdot 2^6 + 0 \cdot 2^5 + 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1$ . In binary, then, the number would be written as 1010101. In an 8-bit register, this could be stored as 01010101, while in a 32-bit register, it would be 00000000000000000000000001010101.

It's possible to do arithmetic on these binary numbers using the same strategies and algorithms that elementary students use for solving base 10 problems. In fact, it's even easier, as the addition and multiplication tables are much smaller and simpler! Because there are only two digits, 0 and 1, there are only four entries in the tables, as can be seen in figure 1.9. Just remember that, when adding in binary (base 2), every time the result is a 2, it generates a carry (just as every 10 generates a carry in base 10). So the result of adding 1 + 1 in base 2 is not 2, but 0 carry the 1 or 10.

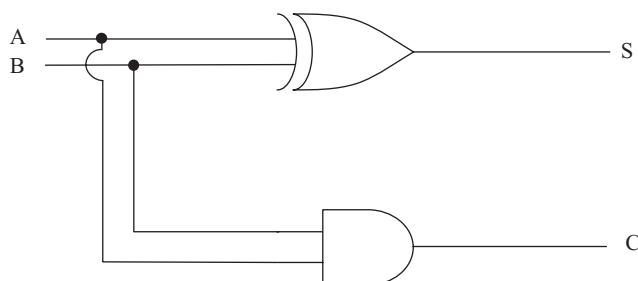

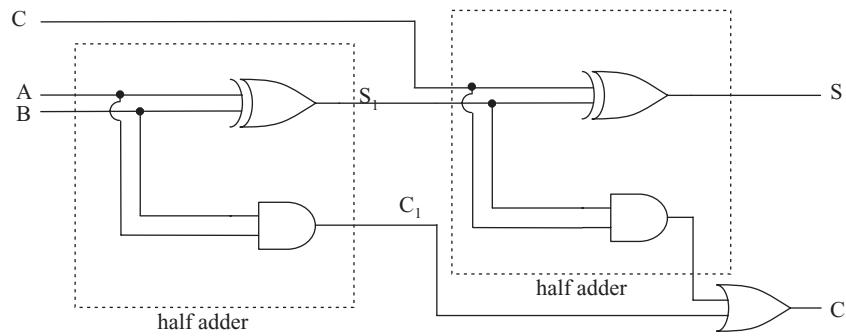

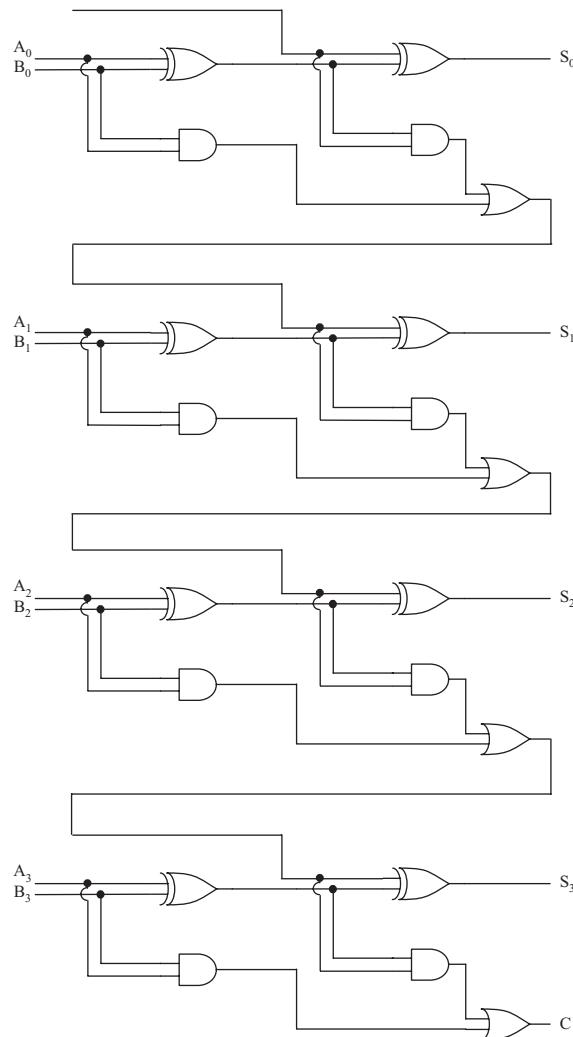

Inspection of the tables reveals the fundamental connection between binary arithmetic and Boolean algebra. The multiplication table is identical to the AND of the two factors. Addition, of course, can potentially generate two numbers: a one-digit sum and a possible carry. There is a carry if and only if the first number is a 1 and the second number is a 1; in other words, the carry is simply the AND of the two addends, while the sum (excluding the carry) is 1 if the first number is 1 or the second number is 1, but not both: the XOR of the two addends. By building an

|                                                                                        |                                                                                           |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| $  \begin{array}{c cc}  + & 0 & 1 \\  \hline  0 & 0 & 1 \\  1 & 1 & 10  \end{array}  $ | $  \begin{array}{c cc}  \cdot & 0 & 1 \\  \hline  0 & 0 & 0 \\  1 & 0 & 1  \end{array}  $ |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

**Figure 1.9** Addition and multiplication tables for binary (base 2) arithmetic

appropriate collection of AND and XOR gates, the computer can add or multiply any numbers within the expressive power of the registers.

How large a number, then, can be stored in an 8-bit register? The smallest possible value is obviously 00000000, representing the number 0. The largest possible value, then, would be 11111111, the number 255. Any integer in this range can be represented easily as an 8-bit quantity. For 32-bit registers, the smallest value is still 0, but the largest value is just over 4.2 billion.

Although computers have no difficulty interpreting long binary numbers, humans often do. For example, is the 32-bit number 00010000000000000000000000000000 the same as the number (deep breath here) 00010000000000000000000000000000? (No, they are different. There are sixteen 0s between the 1s in the first number and only fifteen in the second.) For this reason, when it is necessary (rarely, one hopes) to deal with binary numbers, most programmers prefer to use **hexadecimal** (base 16) numbers instead. Since  $16 = 2^4$ , every block of 4 bits (sometimes called a **nybble**) can be represented as a single base 16 “digit.” Ten of the 16 hexadecimal digits are familiar to us as the numbers 0 through 9, representing the patterns 0000 through 1001. Since our normal base 10 uses only 10 digits, computer scientists have co-opted the letters A through F to represent the remaining patterns (1010, 1011, 1100, 1101, 1110, 1111; see table 1.1 for the complete conversion list). Nowadays, this is about the only use that people have for hexadecimal numbers: to specify and abbreviate long lists of bitstring values such as might be used in cryptography or networking. The two numbers above are clearly different when converted to base 16:

|                                                                                                                                                                   |                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $  \begin{array}{cccccccc c}  0001 & 0000 & 0000 & 0000 & 0000 & 1000 & 0000 & 0000 & = 0x10000800 \\  1 & 0 & 0 & 0 & 0 & 8 & 0 & 0 & \\  \hline  \end{array}  $ | $  \begin{array}{cccccccc c}  0001 & 0000 & 0000 & 0000 & 0001 & 0000 & 0000 & 0000 & = 0x10001000 \\  1 & 0 & 0 & 0 & 1 & 0 & 0 & 0 & \\  \hline  \end{array}  $ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex | Binary | Hex | Binary | Hex | Binary | Hex | Binary |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 0   | 0000   | 4   | 0100   | 8   | 1000   | C   | 1100   |

| 1   | 0001   | 5   | 0101   | 9   | 1001   | D   | 1101   |

| 2   | 0010   | 6   | 0110   | A   | 1010   | E   | 1110   |

| 3   | 0011   | 7   | 0111   | B   | 1011   | F   | 1111   |

**Table 1.1** Hexadecimal  $\leftrightarrow$  binary digit conversions

By convention in many computer languages (including Java, C, and C++), hexadecimal numbers are written with an initial “0x” or “0X.” We follow that convention here, so the number 1001 refers to the decimal value one thousand one. The value 0x1001 would refer to  $16^3 + 1$ , the decimal value four thousand ninety-seven. (Binary quantities will be clearly identified as such in the text. Also, on rare occasions, some patterns will be written as **octal**, or base 8, numbers. In C, C++, or Java, these numbers are written with a leading 0, so the number 01001 would be an octal value equivalent to 513. This is a rather unfortunate convention, since almost no one uses octal for any reason, but the tradition continues.) Note that 0 is still 0 (and 1 is still 1) in any base.

### Base Conversions

Converting from a representation in one base to another can be a tedious but necessary task. Fortunately, the mathematics involved is fairly simple. Converting from any other base into base 10, for example, is simple if you understand the notation. The binary number 110110, for instance, is defined to represent  $2^5 + 2^4 + 2^2 + 2^1$ ,  $32 + 16 + 4 + 2$ , or 54. Similarly, 0x481 is  $4 \cdot 16^2 + 8 \cdot 16^1 + 1$ ,  $1024 + 128 + 1$ , or (decimal) 1153.

An easier way to perform the calculation involves alternating multiplication and addition. The binary number 110110 is, perhaps obviously, twice the binary value of 11011. (If this isn’t obvious, notice that the base 10 number 5280 is 10 times the value of 528.) The binary number 11011 is, in turn, twice 1101 plus 1. Thus, one can simply alternate multiplying by the base value and adding the new digit. Using this system, binary 110110 becomes

$$((((((1 \cdot 2) + 1) \cdot 2) + 0) \cdot 2) + 1) \cdot 2) + 0$$

which simple arithmetic will confirm is 54. Similarly 0x481 is

$$(((4 \cdot 16) + 8) \cdot 16) + 1$$

which can be shown to be 1153.

If alternating multiplication and addition will convert to base 10, then it stands to reason that alternating division and subtraction can be used to convert from base 10 to binary. Subtraction is actually implicit in the way we will be using division. When dividing integers by integers, it’s rather rare that the answer is exact; normally there’s a remainder that must be implicitly subtracted from the dividend. These remainders are exactly the base digits. Using 54 again as our example, the remainders generated when we repeatedly divide by 2 will generate the necessary binary digits.

$$54 \div 2 = 27r0$$

$$27 \div 2 = 13r1$$

$$13 \div 2 = 6r1$$

$$6 \div 2 = 3r0$$

$$3 \div 2 = 1r1$$

$$1 \div 2 = 0r1$$

The boldface numbers are, of course, the bits for the binary digits of 54 (binary 110110). The only tricky thing to remember is that, in the multiplication procedure, the digits are entered in the normal order (left to right), so in the division procedure, unsurprisingly, the digits come out in right-to-left order, backward. The same procedure works for base 16 (or indeed for base 8, base 4, or any other base):

$$1153 \div 16 = 72\mathbf{r}1$$

$$72 \div 16 = 4\mathbf{r}8$$

$$4 \div 16 = 0\mathbf{r}4$$

Finally, the most often used and perhaps the most important conversion is direct (and quick) conversion between base 2 and base 16, in either direction. Fortunately, this is also the easiest. Because 16 is the fourth power of 2, multiplying by 16 is really just multiplying by  $2^4$ . Thus, every hexadecimal digit corresponds directly to a group of 4 binary digits. To convert from hexadecimal to binary, as discussed earlier, simply replace each digit with its 4-bit equivalent. To convert from binary to hexadecimal (hex), break the binary number into groups of 4 bits (starting at the right) and perform the replacement in the other direction. The complete conversion chart is (re)presented as table 1.2.

| Hex | Binary | Hex | Binary | Hex | Binary | Hex | Binary |

|-----|--------|-----|--------|-----|--------|-----|--------|

| 0   | 0000   | 4   | 0100   | 8   | 1000   | C   | 1100   |

| 1   | 0001   | 5   | 0101   | 9   | 1001   | D   | 1101   |

| 2   | 0010   | 6   | 0110   | A   | 1010   | E   | 1110   |

| 3   | 0011   | 7   | 0111   | B   | 1011   | F   | 1111   |

**Table 1.2** Hexadecimal  $\leftrightarrow$  binary digit conversions

(copy of table 1.1)

So, for example, the binary number 100101101100101 would be broken up into 4-bit nybbles, starting from the right, as 100 1011 0110 0101. (Please note that I cheated: the number I gave you has only 15 bits, so one group of 4 isn't complete. This group will always be on the far left and will be padded out with 0s, so the "real" value you will need to convert will be 0100 1011 0110 0101.) If you look these four values up in the table, you will find that they correspond to the values 4, B, 6, and 5. Therefore, the corresponding hexadecimal number is 0x4B65.

Going the other way, the hexadecimal number 0x18C3 would be converted to the four binary groups 0001 (1), 0100 (8), 1100 (C) and 0101 (3), which are put together to give the binary quantity 0001010011000101.

A similar technique would work for octal (base 8) with only the first two columns of table 1.1 and using only the last 3 (instead of 4) bits of the binary entries, as shown in table 1.3. Using these notations and techniques, you can represent any nonnegative integer in a sufficiently large register and interpret it in any base we've discussed. With a bit of creativity and flair, you can even adapt these techniques to oddball bases like base 3 or base 7.

| Hex | Binary | Hex | Binary |

|-----|--------|-----|--------|

| 0   | 000    | 4   | 100    |

| 1   | 001    | 5   | 101    |

| 2   | 010    | 6   | 110    |

| 3   | 011    | 7   | 111    |

**Table 1.3** Octal  $\leftrightarrow$  binary digit conversions

### Signed Representations

In the real world, there is often a use for negative numbers. If the smallest possible value stored in a register is 0, how can a computer store negative values? The question, oddly enough, is not one of storage but of interpretation. Although the maximum number of storable patterns is fixed (for a given register size), the programmer can decide to interpret some patterns as meaning negative values. The usual method for doing this is to use an interpretation known as **two's complement notation**.

It's a common belief (you can even see it in the film *Ferris Bueller's Day Off*) that if you drive a car in reverse, the odometer will run backward and apparently take miles off the engine. I don't know if it works or not—it didn't work for Ferris—but [Howstuffworks.com](http://auto.howstuffworks.com/odometer1.htm)<sup>1</sup> says that it should have. Imagine for a moment that it did. Suppose I took a relatively new car (say, with 10 miles on it) and ran it in reverse for 11 miles. What would the odometer say?

Well, the odometer *wouldn't* say  $-1$  miles. It would probably read 999,999 miles, having turned over at 000,000. But if I then drove another mile forward, the odometer would turn over (again) to 000,000. We can implicitly define the number  $-1$  as the number that, when 1 is added to it, results in a 0.

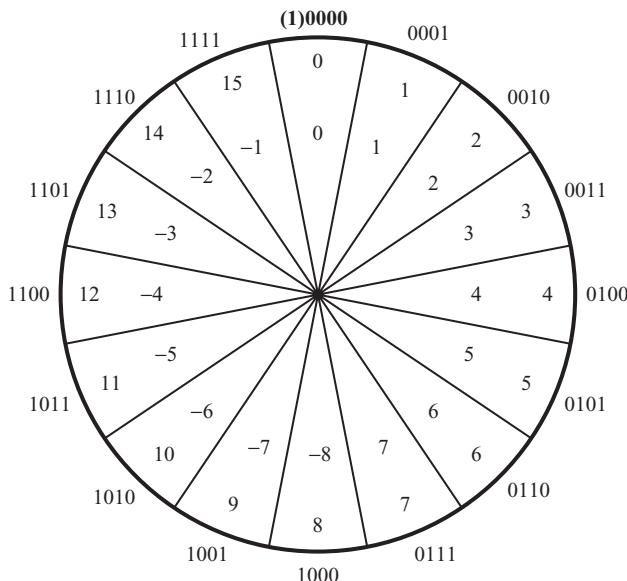

This is how two's complement notation works; negative numbers are created and manipulated by counting backward (in binary) from a register full of 0s, as in figure 1.10. Numbers in which the first bit is a 0 are interpreted as positive numbers (or 0), while numbers in which the first bit is a 1 are interpreted as negative. For example, the number 13 would be written in (8-bit) binary as 00001101 (hexadecimal 0x0D), while the number  $-13$  would be 11110011 (0xF3). These patterns are called **signed** numbers (integers, technically) as opposed to the previously defined **unsigned** numbers. In particular, the pattern 0xF3 is the **two's complement notation** representation of  $-13$  (in an 8-bit register).

How do we get from 0xF3 to  $-13$ ? Beyond the leading 1, there appears to be no similarity between the two representations. The connection is a rather subtle one based on the above definition of negative numbers as the inverses of positive numbers. In particular,  $13 + -13$  should equal 0. Using the binary representations above, we note that

$$\begin{array}{r}

00001101 & 13 \\

+ 11110011 & -13 \text{ in two's-complement notation} \\

\hline

10000000 & 0 \text{ plus an overflow/carry}

\end{array}$$

<sup>1</sup> <http://auto.howstuffworks.com/odometer1.htm>

**Figure 1.10** Structure of 4-bit signed integer representation

However, the 9-bit quantity 100000000 (0x100) cannot be stored in only an 8-bit register! Like a car odometer that rolls over when the mileage becomes too great, an 8-bit register will **overflow** and lose the information contained in the ninth bit. The resulting stored pattern is therefore 00000000 or 0x00, which is the binary (and hex equivalent of 0. Using this method, we can see that the range of values stored in an 8-bit register will vary from  $-128$  (0x80) to  $+127$  (0x7F). Approximately half of the values are positive and half are negative, which in practical terms is about what people typically want. Figure 1.10 shows that, in general, there is one more negative number than positive number, because the number opposite 0 on the figure is negative.

This demonstration relies critically on the use of an 8-bit register. In a 32-bit register, a much larger value is necessary to produce overflow and wrap around to 0. The 32-bit two's complement representation of  $-13$  would not be 0xF3, but 0xFFFFFFFF3. In fact, viewed as a 32-bit number, 0xF3 would normally be interpreted as 0x000000F3, which isn't even negative, since the first bit isn't a 1.

Calculating the two's complement representation of a number (for a given fixed register size) by hand is not difficult. Notice first that the representation of  $-1$ , for any register size, will always be a register containing all 1s. Adding 1 to this number will produce overflow and a register full of 0s. For any given bit pattern, if you reverse every individual bit (each 1 becomes a 0, each 0 becomes a 1, while preserving the original order—this operation is sometimes called the **bitwise NOT**, because it applies a NOT to every individual bit) and add the resulting number to the original, the result will always give you a register full of 1s. (Why?) This inverted pattern (sometimes called the “one's complement” or just the “complement”), added to the original pattern, will yield a sum

of  $-1$ . And, of course, adding one more will give you a  $-1 + 1$ , or  $0$ . This inverted pattern plus  $1$ , then, will give you the two's complement of the original number.

$$\begin{array}{r}

00001101 \quad (= 13) \\

11110010 \quad (\text{inverted}) \\

+ \quad \quad \quad 1 \\

\hline

11110011 \quad (= -13)

\end{array}$$

Note that repeating the process a second time will negate the negation.

$$\begin{array}{r}

11110011 \quad (= -13) \\

00001100 \quad (\text{inverted}) \\

+ \quad \quad \quad 1 \\

\hline

00001101 \quad (= 13)

\end{array}$$

This process will generalize to any numbers and any (positive) register size. Subtraction will happen in exactly the same way, since subtracting a number is exactly the same as adding its negative.

### *Floating Point Representation*

In addition to representing signed integers, computers are often called upon to represent fractions or quantities with decimal points. To do this, they use a modification of standard scientific notation based on powers of 2 instead of powers of 10. These numbers are often called **floating point** numbers because they contain a “decimal” point that can float around, depending upon the representation.

Starting with the basics, it’s readily apparent that any integer can be converted into a number with a decimal point just by adding a decimal point and a lot of 0s. For example, the integer  $5$  is also  $5.000\dots$ , the number  $-22$  is also  $-22.0000\dots$ , and so forth. This is also true for numbers in other bases (except that technically the “decimal” point refers to base 10; in other bases, it would be called a “radix” point). So the (binary) number  $1010$  is also  $1010.0000\dots$ , while the (hexadecimal) number  $0x357$  is also  $0x357.0000\dots$ .

Any radix point number can also be written in scientific notation by shifting the point around and multiplying by the base a certain number of times. For example, Avogadro’s number is usually approximated as  $6.023 \cdot 10^{23}$ . Even students who have forgotten its significance in chemistry should be able to interpret the notation—Avogadro’s number is a 24-digit ( $23 + 1$ ) number whose first four digits are 6, 0, 2, 3, or about 602,300,000,000,000,000,000,000. Scientific notation as used here has three parts: the **base** (in this case, 10), the **exponent** (23), and the **mantissa** (6.023). To interpret the number, one raises the base to the power of the exponent and multiplies by the mantissa. Perhaps obviously, there are many different mantissa/exponent sets that would produce the same number; Avogadro’s number could also be written as  $6023 \cdot 10^{20}$ ,  $60.23 \cdot 10^{22}$ , or even  $0.6023 \cdot 10^{24}$ .

Computers can use the same idea, but using binary representations. In particular, note the patterns in table 1.4. Multiplying the decimal number by 2 shifts the representation 1 bit to the

left, while dividing by 2 shifts it 1 bit to the right. Alternatively, a form of scientific notation applies where the same bit pattern can be shifted (and the exponent adjusted appropriately), as in table 1.4.

| Decimal | Binary integer | Binary radix     | Scientific notation       |

|---------|----------------|------------------|---------------------------|

| 5       | 00000101       | 00000101.0000... | 1.01 (binary) $\cdot 2^2$ |

| 10      | 00001010       | 00001010.0000... | 1.01 (binary) $\cdot 2^3$ |

| 20      | 00010100       | 00010100.0000... | 1.01 (binary) $\cdot 2^4$ |

| 40      | 00101000       | 00101000.0000... | 1.01 (binary) $\cdot 2^5$ |

**Table 1.4** Exponential notation with binary numbers

We extend this to represent noninteger floating point numbers in binary the usual way, as expressed in table 1.5. The number 2.5, for example, being exactly half of 5, could be represented as the binary quantity 10.1 or as the binary quantity 1.01 times  $2^1$ . 1.25 would be (binary) 1.01 or 1.01 times  $2^0$ . Using this sort of notation, any decimal floating point quantity has an equivalent binary representation.

| Decimal | Binary | Binary real  | Scientific notation            |

|---------|--------|--------------|--------------------------------|

| 5       | 101    | 00101.000... | 1.0100 (binary) $\cdot 2^2$    |

| 2.5     |        | 00010.100... | 1.0100 (binary) $\cdot 2^1$    |

| 1.25    |        | 00001.010... | 1.0100 (binary) $\cdot 2^0$    |

| 0.6125  |        | 00000.101... | 1.0100 (binary) $\cdot 2^{-1}$ |

**Table 1.5** Exponential notation with binary fractions

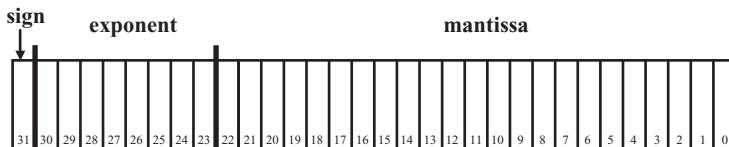

The Institute for Electrical and Electronic Engineers (IEEE) has issued a series of specification documents describing standardized ways to represent floating point numbers in binary. One such standard, IEEE 754-1985, describes a method of storing floating point numbers as 32-bit words as follows (and as illustrated in figure 1.11):

**Figure 1.11** IEEE 32-bit floating point storage: sign, exponent, mantissa

Number the 32 bits of the word starting from bit 31 at the left down to bit 0 at the right. The first bit (bit 31) is the **sign** bit, which (as before) tells whether the number is positive or negative. Unlike two's complement notation, this sign bit is the only way in which two numbers of equal magnitude differ.

The next 8 bits (bits 30–23) are a “biased” **exponent**. It would make sense to use the bit pattern 0000000 to represent  $2^0$  and 0000001 to represent  $2^1$ , but then one couldn’t represent small values like 0.125 ( $2^{-3}$ ). It would also make sense to use 8-bit two’s complement notation,

but that's not what the IEEE chose. Instead, the IEEE specified the use of the unsigned numbers 0..255, but the number stored in the exponent bits (the representational exponent) is a “biased” exponent, actually 127 higher than the “real” exponent. In other words, a real exponent of 0 will be stored as a representational exponent of 127 (binary 01111111). A real exponent of 1 would be stored as 128 (binary 10000000), and a stored exponent of 00000000 would actually represent the tiny quantity  $2^{-127}$ . The remaining 23 bits (bits 22–0) are the mantissa with the decimal point—technically called the **radix point**, since we're no longer dealing with base 10—placed conventionally immediately after the first binary digit. This format, using a fixed number of positions in front of the radix point, is sometimes called **normalized form**.

Thus, for normal numbers, the value stored in the register is the value

$$(-1)^{\text{sign bit}} \cdot \text{mantissa} \cdot 2^{\text{real exponent} + 127}$$

A representational exponent of 127, then, means that the mantissa is multiplied by 1 (a corresponding real exponent of 0, hence a multiplier of  $2^0$ ), while an exponent of 126 means that the fraction is multiplied by  $2^{-1}$  or 0.5, and so forth.

Actually, there is a micro-lie in the above formula. Because the numbers are in binary, the first nonzero digit has to be a 1 (there aren't any other choices that aren't 0!). Since we know that the first digit is a 1, we can leave it out and use the space freed up to store another digit whose value we didn't know beforehand. So the real formula would be

$$(-1)^{\text{sign bit}} \cdot 1.\text{mantissa} \cdot 2^{\text{real exponent} + 127}$$

As a simple example, the decimal number 2.0 in binary is  $1.0 \cdot 2^1$ . Representing this as an IEEE floating point number, the sign bit would be 0 (a positive number), the mantissa would be all 0s (and an implicit leading 1), while the exponent would be  $127 + 1$ , or 128, or binary 10000000. This would be stored in the 32-bit quantity

|      |          |                              |

|------|----------|------------------------------|

| 0    | 10000000 | 0000000000000000000000000000 |

| sign | exponent | mantissa                     |

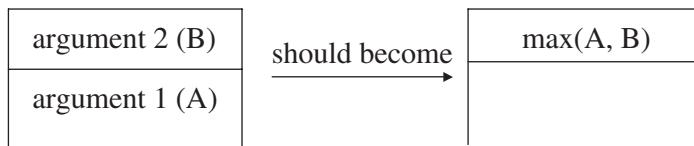

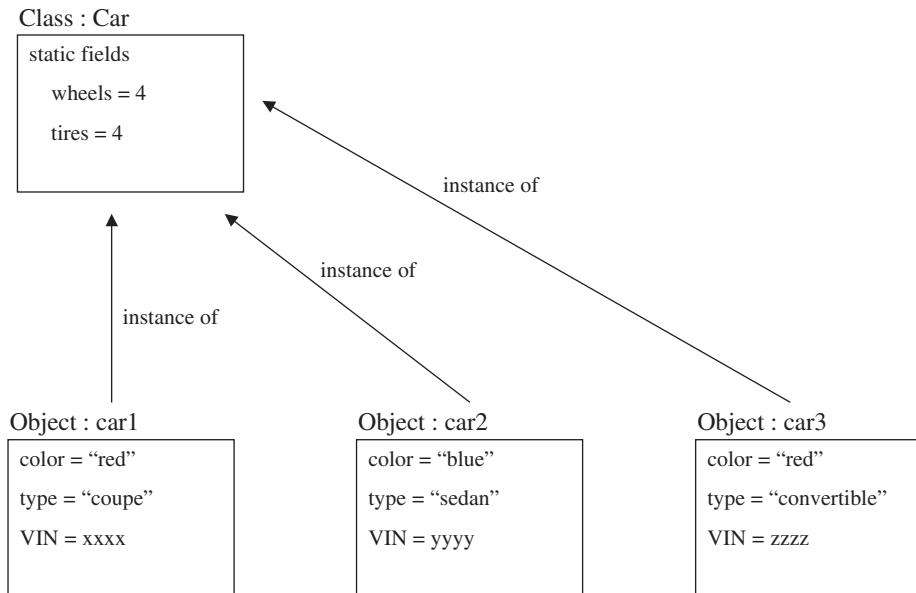

This same bit pattern could be written as the hexadecimal number 0x40000000.